Innovation for the next generation

## **ML1016E-CR**

53.1 GBd PAM4 Optical and Electrical Clock Recovery Module

53.125 GBd PAM4 400GBASE-DR4/FR4/LR4 & 100GBASE-DR1/FR1 transceiver testing | Ideal for 100G Lambda MSA transceivers | Triggers ML4015E Optical Scope for Optical Transmitter TDECQ measurement as well as any other reference scope.

## Summary

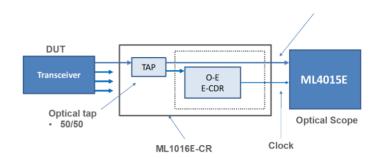

The ML1016E-CR is a 53.125 GBd PAM4 Optical Clock Recovery solution ideally suited for 100G Lambda MSA optical measurements. The recovered clock can trigger the ML4015E Optical Scope and other reference scopes to perform 53.125 GBd PAM4 optical measurements such as TDECQ, OMA, and others. ML1016E-CR supports a variety of standards such as 400GBASE-DR4/FR4/LR4, and 100GBASE-DR/FR/LR.

The optical power range for the ML1016E-CR is from 5dBm down to -2 dBm (spec at the input of the ML1016E-CR).

Considering the 50% splitter ratio, the CDR alone receive half of this power and the lowest is around -5.5 dBm.

# **ML1016E-CR**

# **53.1 GBd PAM4 Optical Clock Recovery Module**

#### Introduction

The ML1016E-CR is a fully featured, cost effective optical CDR solution. The supported wavelength is 1260 to 1650 nm Single-Mode.

#### **Key Features**

The ML1016E-CR is a unique solution for triggering from the same optical channel to have the perfect CLK to data synchronization and to match with the required specs for TP3 testing. Full set of features below:

- Ability to trigger any reference scope

- Correlates well with Tier one CDR solutions, (Correlation data available upon request).

- Only supports 53.125Gbaud

- Fixed loop bandwidth of 4Mhz

- Rate/16 and Rate/32 support.

| Technical Specifications |               |  |  |

|--------------------------|---------------|--|--|

| Input Connector          | FC PC         |  |  |

| Power Input Range        | 5dBm to -2dBm |  |  |

| Jitter                   | 300fs         |  |  |

| Loop Bandwidth           | 4MHz          |  |  |

| Data Rate Support        | 53.125Gbaud   |  |  |

| Modulation               | PAM4          |  |  |

| Supported Clock Rate     | /16 & /32     |  |  |

A complete set of APIs and a dozen of example code to speed up integration under Linux and Windows, using Python, LabView, Matlab and C#.

#### **Typical Applications**

- Production testing of 400G transceivers

- Optical transceiver test

- Transceiver manufacturing test

- Transceiver evaluation and validation

- Incoming inspection of transceivers

- Targeted application: PAM4 53Gbaud

#### **Mechanical Dimensions**

The ML1016E-CR is a benchtop instrument that also fits in a 19-inch 2U rack. MultiLane also supplies the needed brackets.

### **Ordering Information**

| Option      | Description                               |

|-------------|-------------------------------------------|

| ML1016E-CR- | Standalone CR                             |

| OPT-53      | Optical Only 53Gbaud/28Gbaud              |

| E-53        | Electrical Only 53Gbaud/28Gbaud           |

| OPT-E-53    | Fully Loaded Optical + Electrical 53Gbaud |

| 3YW         | 3 Years Warranty                          |

| 5YW         | 5 Years Warranty                          |

| EXP1        | Extended Warranty Plan – 1 Year           |

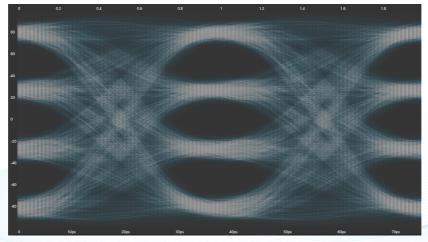

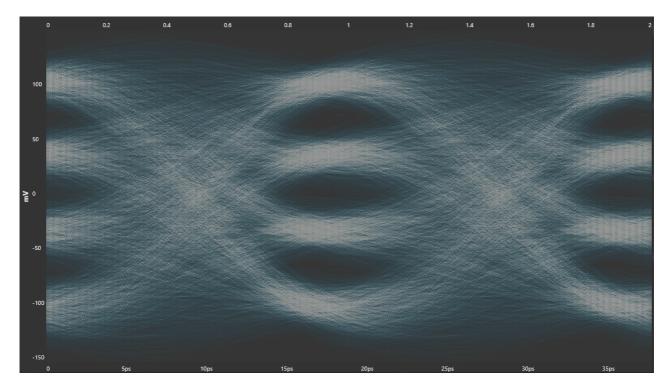

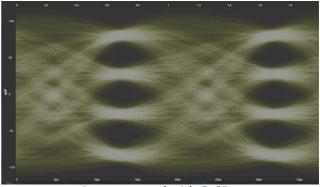

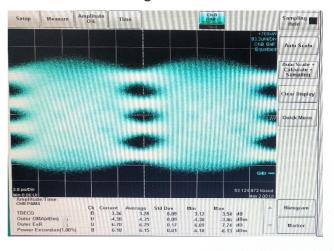

#### Annex A: Test Results at 53.125 GBd PAM4

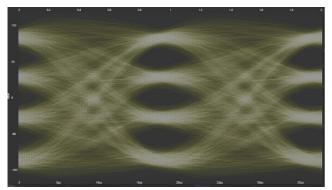

#### **Annex B: Correlation**

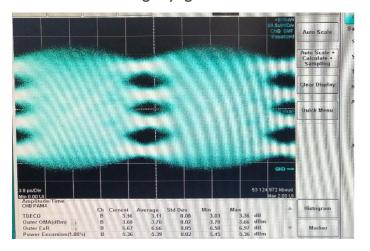

Data captured with direct clock from BERT

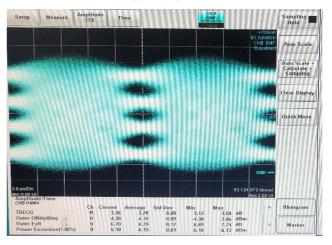

Data captured with O-CR

As can be seen from the data above, the performance of the O-CR is almost identical to the performance with direct clocking from the BERT (Line Side synchronous Trigger).

## High TDECQ Transceiver

Using Keysight CDR

Using Keysight CDR

|                    | CDR-M<br>(Keysight) | ML1016E-CR<br>(MultiLane) | Offset |

|--------------------|---------------------|---------------------------|--------|

| TDECQ<br>(Current) | 3.16                | 3.36                      | 0.2    |

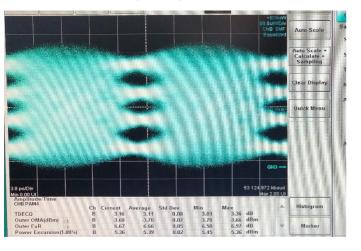

## LOW TDECQ-DR4-400G

Using Keysight CDR

Using 1016E-CR

|                    | CDR-M<br>(Keysight) | ML1016E-CR<br>(MultiLane) | Offset |

|--------------------|---------------------|---------------------------|--------|

| TDECQ<br>(Current) | 1.64                | 1.76                      | 0.12   |