# **ML4004-PAM**

# **PAM4 Time Domain Analyzer**

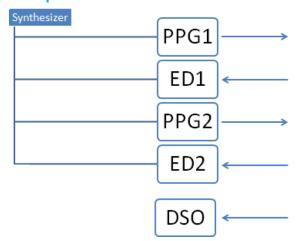

2x56 Gb/s PAM4 BERT with integrated 32GHz DSO

Dual PAM4 PPG and ED

Jitter Analysis

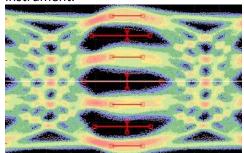

Eye Measurements

Eye Mask Test

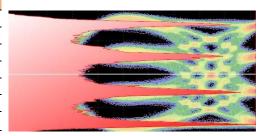

Advanced Pattern Acquisition

# **ML4004-PAM**

2x28 GB/s NRZ or 2x56 GB/s PAM4 BERT with 32 GHz Scope

# **Summary**

The ML4004-PAM is a state of the art dual Channel PAM4 BERT and Digital Sampling Oscilloscope, integrated in an ultra-compact form factor. USB/Ethernet controlled, it performs accurate eyediagram analysis to characterize the quality of transmitters and receivers.

The ML4004-PAM DSO implements a statistical under sampling technique using comprehensive software libraries. It performs various eye and pattern measurements (if the rate is above 6Gbps), mask margin tests and jitter analysis on PAM4 and NRZ signals.

# **Key Features**

PAM4 scope measurements are currently following the latest OIF contribution.

#### **BERT** features

NRZ Bit Rates<sup>1</sup>: 18.6-30.2 Gb/s

PAM4 Bit Rates: 37.2-60 Gb/s

Inner eye amplitude variation (PAM4 mode)

100G FEC KR4 or scaled KP4

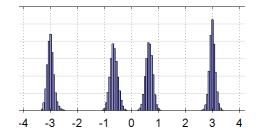

- Histogram and SNR measurements (PAM4 Mode)

- Intuitive comprehensive GUI

- QPRBS13 on the PPG

- User-defined pattern 80 bits or up to 2kb from a .txt file

#### DSO features

- Low intrinsic jitter

- Optional External reference clock input

- SW filters applicable include CTLE, FFE, S-Parameter De-Embedding, Moving Average

- Single ended and differential electrical input

- Eye, histogram and pattern capture in a single instrument.

- PAM4 Measurements

- Statistics histograms and Histogram measurements.

- Integrated synthesizer

- User friendly GUI that enables: zooming, markers, X and Y histograms, statistics, overlays and multiple measurements.

- Load and analyze data that was previously captured in simulation mode

- The DSO tool can operate in a data acquisition only mode where the data is saved on multiple acquisitions for post processing.

- Capability to save statistical measurement, data files and configurations

- Color graded display in eye capture mode

- Insertion loss measurement down to 40 dB

$^{1}$  NRZ bit rates 10 - 15 Gb/s can also be generated on TX0

| PAM4 Measurements         |

|---------------------------|

| Symbol Levels             |

| Vertical Eye Amplitudes   |

| Vertical Eye Openings     |

| Horizontal Eye Openings   |

| Vertical Eye Closure (dB) |

| Openings by BER (soon)    |

| Max, Min, Peak-to-Peak    |

# **Target Applications**

- Interconnect testing, SFP, SFP28, CFP, CFP2, CFP4, QSFP, QSFP28, ...

- Backplane testing

- Interference and Crosstalk testing

- Receiver sensitivity testing

# **Ordering Information**

ML4004-PAM: 2x56 Gb/s PAM4 Bert with 1x 32GHz or 50GHz BW Scope

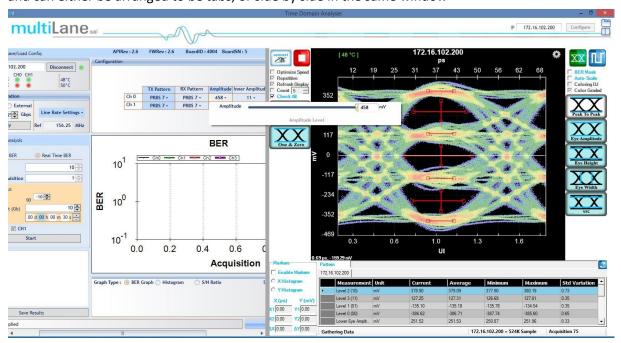

### **Time Domain Analyzer GUI**

The user interface for the ML4004-PAM is an all-new combination of the ML-Bert and ML-DSO programs for either PAM4 or NRZ modes. Both the DSO and Bert functions are accessible by the same IP address, and can either be arranged to be tabs, or side by side in the same window

| Electrical Specifications |                                |                                         |  |

|---------------------------|--------------------------------|-----------------------------------------|--|

| NRZ Mode<br>PPG1/2        | Bit Rates                      | 18.6-30.2 Gbps                          |  |

|                           | TX Amplitude Differential      | 250-1000mV                              |  |

|                           | Patterns                       | PRBS7/9/15/23/31                        |  |

|                           |                                | Square 16 and Square 32                 |  |

|                           | Pre-Emphasis                   | 6 dB                                    |  |

|                           | Pre-Emphasis Resolution        | 10 steps                                |  |

|                           | Equalizing Filter Spacing      | 1UI                                     |  |

|                           | Random Jitter RMS              | 220 fS                                  |  |

|                           | Rise/ Fall Time (20–80%)       | 12 pS                                   |  |

|                           | Output Return Loss up to 10GHz | -15 dB                                  |  |

|                           | Output Return Loss (16-25GHz)  | -10 dB                                  |  |

|                           | Error Detector Phase Margin    | 5 pS                                    |  |

|                           | Error Detector damage level    | 1200 mV Diff                            |  |

| NRZ Mode<br>ED1/2         | Input CTLE Dynamic Range       | 10 dB                                   |  |

|                           | TX/RX and clock connectors     | 2.92 mm K Connectors                    |  |

|                           | Deference cleak Output         | Rate / 66 for bit rates 10 to 15G       |  |

|                           | Reference clock Output         | Rate / 165 for 18.6 to 30.2 G           |  |

|                           | Bit Rates                      | 37.2-60 Gbps                            |  |

|                           | TX Amplitude Differential      | 250-1000 mV                             |  |

|                           | Patterns                       | PRBS7/9/11/15/23/31/Square_16/Square_32 |  |

|                           |                                | User Pattern 80 bits/ QPRBS13 / 16640   |  |

| PAM4                      |                                | symbols in .txt file format             |  |

| Mode                      | Pre-Emphasis                   | 6 dB                                    |  |

| PPG1/2                    | Pre-Emphasis Resolution        | 10 steps                                |  |

|                           | Equalizing Filter Spacing      | 1UI                                     |  |

|                           | Random Jitter RMS              | 200 fS                                  |  |

|                           | Rise/ Fall Time (20–80%)       | 12 pS                                   |  |

|                           | Output Return Loss up to 10GHz | -15 dB                                  |  |

|                           | Output Return Loss (16-25GHz)  | -10 dB                                  |  |

| PAM4<br>Mode<br>ED1/2     | Error Detector Phase Margin    | 5 pS                                    |  |

|                           | Error Detector Maximum Input   | 1200 mV Diff                            |  |

|                           | Error Detector linear range    | 250 – 400 mVpp diff.                    |  |

|                           | Input CTLE Dynamic Range       | 10 dB adaptive                          |  |

|                           | TX/RX and clock connectors     | 2.92 mm K Connectors                    |  |

|                           | Reference clock Output         | Rate / 165                              |  |

|                           | Input Bandwidth                | 32 GHz or 50 GHz                        |  |

| DSO                       | Input Amplitude (Single ended) | AC: 600 mVpp Single-ended               |  |

|                           | Input Rise / Fall Time         | 14 ps (12ps for 50 GHz variant)         |  |

|                           | Diff. Input Return Loss        | Better than 10 dB                       |  |

|  | Vertical Resolution              | 12 bits       |

|--|----------------------------------|---------------|

|  | Clock Input Range (Normal Mode)  | 50 - 710 MHz  |

|  | Clock Input Range (Bypass Mode)  | 50 - 125 MHz  |

|  | Clock Input Amplitude            | 200 - 1000 mV |

|  | Input Impedance                  | 50 Ω          |

|  | Intrinsic Jitter (excluding DDJ) | 200 fS        |

|  | Amplitude Error                  | 5 mV          |

|  | Data Format Support              | NRZ/PAM4      |

|  | PRBS Pattern Capture             | up to PN11    |

|  | Spurious-Free Dynamic Range      | 8 bits        |

|  | Temperature range                | 0-65C         |

|  | Power Requirements               | 1.2A @ 12V    |

|  | Memory Depth                     | 256K sample   |