## **USER GUIDE**

## **Common Management Interface Kit**

CMIS GUI User Guide – CMIS Rev3.0/4.0 Compliant Revision 0.2 October 2021

QSFP-DD Host – QSFP Host – DSFP Host – SFP-DD Host – OSFP Host

Innovation for the next generation

Copyright © MultiLane Inc. All rights reserved. Licensed software products are owned by MultiLane Inc. or its suppliers and are protected by United States copyright laws and international treaty provisions.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013, or subparagraphs (c)(1) and (2) of the Commercial Computer Software -- Restricted Rights clause at FAR 52.227-19, as applicable.

MultiLane Inc. products are covered by U.S. and foreign patents, issued and pending. Information in this publication supersedes that in all previously published material. Specifications and price change privileges reserved.

#### **General Safety Summary**

Review the following safety precautions to avoid injury and prevent damage to this product or any products connected to it. To avoid potential hazards, use this product only as specified.

Only qualified personnel should perform service procedures.

While using this product, you may need to access other parts of the system. Read the General Safety Summary in other system manuals for warnings and cautions related to operating the system.

#### To Avoid Fire or Personal Injury

**Use Proper Power Cord.** Only use the power cord specified for this product and certified for the country of use.

**Observe All Terminal Ratings.** To avoid fire or shock hazard, observe all ratings and markings on the product. Consult the product manual for further ratings information before making connections to the product.

Do not apply a potential to any terminal, including the common terminal that exceeds the maximum rating of that terminal.

#### Do Not Operate Without Covers.

Do not operate this product with covers or panels removed.

**Avoid Exposed Circuitry.** Do not touch exposed connections and components when power is present.

#### Do Not Operate with Suspected Failures.

If you suspect there is damage to this product, have it inspected by qualified service personnel.

Do Not Operate in Wet/Damp Conditions. Do Not Operate in an Explosive Atmosphere. Keep Product Surfaces Clean and Dry

Caution statements identify conditions or practices that could result in damage to this product or other property.

## Table of Contents

| 1. | Installation & Running                                               |  |

|----|----------------------------------------------------------------------|--|

| 2. | CMIS Version                                                         |  |

|    |                                                                      |  |

| 3. | Communication                                                        |  |

| 4. | GUI Sections                                                         |  |

|    | .1 Monitor                                                           |  |

|    | .2 Interrupt Masks                                                   |  |

|    | .3 Controls                                                          |  |

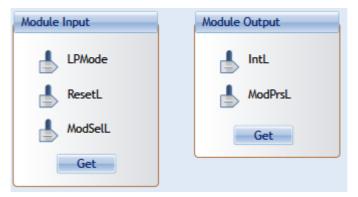

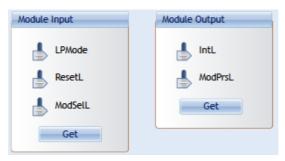

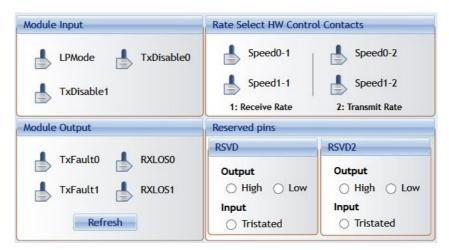

|    | .4 Low Speed Signals                                                 |  |

|    | 4.4.1 QDD Family                                                     |  |

|    | 4.4.2 OSFP Family                                                    |  |

|    | 4.4.3 DSFP Family                                                    |  |

|    | 4.4.4 QSFP Family<br>4.4.5 SFP-DD Family                             |  |

|    | 4.4.5 SFP-DD Family                                                  |  |

|    |                                                                      |  |

|    | .6 Options Available<br>.7 Load/Save MSA                             |  |

|    | .8 Load/Save MISA                                                    |  |

|    | .9 I2C R/W                                                           |  |

|    | .10 QDD MXP                                                          |  |

|    | .11 I2C R/W Advanced                                                 |  |

|    | .12 Command Data Block (CDB) Message Communication                   |  |

|    | 12.1 CDB Commands                                                    |  |

|    | CMD 0000h Query Status                                               |  |

|    | <ul> <li>CMD 0001h Enter Password</li> </ul>                         |  |

|    | <ul> <li>CMD 0002h Change Password</li></ul>                         |  |

|    | <ul> <li>CMD 0003h Enable/Disable Password Protection</li> </ul>     |  |

|    | <ul> <li>CMD 0004h General Abort</li> </ul>                          |  |

|    | <ul> <li>CMD 0380h Loopbacks</li> </ul>                              |  |

|    | .12.2 CDB Feature and Capabilities Commands                          |  |

|    | CMD 0040h Module Features                                            |  |

|    | <ul> <li>CMD 0042h Performance Monitoring</li> </ul>                 |  |

|    | CMD 0043h Bert and diagnostics                                       |  |

|    | CMD 0041h Read FW Features                                           |  |

|    | .12.3 CDB Firmware Download Commands                                 |  |

|    | <ul> <li>CMD 0101h, 0103h, 0107h Program LPL</li> </ul>              |  |

|    | CMD 0101h, 0104h, 0107h Program EPL                                  |  |

|    | <ul> <li>CMD 0101h, 0105h, 0107h Read Image LPL</li> </ul>           |  |

|    | <ul> <li>CMD 0101h, 0106h, 0107h Read Image EPL</li> </ul>           |  |

|    | CMD 0102h Abort FW download                                          |  |

|    | <ul> <li>CMD 0109h Run image</li> </ul>                              |  |

|    | CMD 010Ah Commit image                                               |  |

|    | <ul> <li>CMD 0108h Copy image A to B/B to A</li> </ul>               |  |

|    | <ul> <li>CMD 0100h Get FW Info</li> </ul>                            |  |

|    | .12.4 CDB Performance/Data Monitoring Commands                       |  |

|    | CMD 0200h PM Controls                                                |  |

|    | CMD 0201h PM Feature Information                                     |  |

|    | <ul> <li>CMD 0280h Data Monitoring and Recording Controls</li> </ul> |  |

|    | <ul> <li>CMD 0281h Data monitoring and recording</li> </ul>          |  |

|    | CMD 0290h Temperature Histogram                                      |  |

|    | CMD 0210h, 0211h Get Module PM LPL/EPL                               |  |

|    | <ul> <li>CMD 0212h, 0213h Get PM Host Side LPL/EPL</li> </ul>        |  |

|    | CMD 0214h, 0214h Get PM Media Side LPL/EPL                           |  |

|    | CMD 0216h, 0217h Get Data Path PM LPL/EPL                            |  |

## **Revision Control**

| Revision number | Description                                                | Release Date |

|-----------------|------------------------------------------------------------|--------------|

| 0.1             | <ul> <li>Initial version</li> </ul>                        | 4/20/2020    |

| 0.22            | <ul><li>Added CDB Feature</li><li>Format updates</li></ul> | 10/12/2021   |

## List of Acronyms

| Acronym | Definition                      |

|---------|---------------------------------|

| CMIS    | Common Management Interface Kit |

| CDB     | Command Data Block              |

| BW      | Bandwidth                       |

| BERT    | Bit Error Rate Tester           |

| Conf    | Configuration                   |

| DUT     | Device Under Test               |

| FEC     | Forward Error Correction        |

| FW      | Firmware                        |

| GBd     | Gigabaud                        |

| Gbps    | Gigabits per Second             |

| GUI     | Graphical User Interface        |

| HW      | Hardware                        |

| SI      | Signal Integrity                |

| Sim     | Simulation                      |

| SW      | Software                        |

### Introduction

The ML-CMIS GUI is a common software interface that allows to communicate with, operate and control various MCBs boards. It allows to utilize a common software across a variety of form factors. The ML-CMIS GUI communicate with the host board through USB connection. The communication is established after installing the proper driver of the target host.

The ML-CMIS GUI allows to communicate on multiple hosts simultaneously, by assigning different USB instance to each host.

The various hosts operating with the ML-CMIS GUI are listed below:

- QDD Host

- QDD host

- OSFP host

- QSFP host

- SFP-DD host

- DSFP host

## **GUI** Introduction

#### 1. Installation & Running

The GUI installation file is available on the website. User could download it under the target product page.

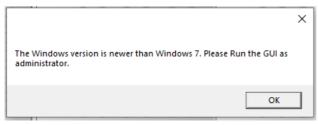

To install the GUI, simply double-click on the installer file, and follow the instructions. For Windows version newer than Windows 7 the GUI must be run as administrator. A message box will pop-up for confirmation.

Figure 1: Pop-up message

After the GUI runs properly, a window will open as shown below.

|       | _    |           |            |        |        |                  |           |          |          | Com      | munication       |            |          |             |          |          |                 |

|-------|------|-----------|------------|--------|--------|------------------|-----------|----------|----------|----------|------------------|------------|----------|-------------|----------|----------|-----------------|

| ulti  | Lar  |           |            |        | ~~~    | $\bigwedge \sim$ | <u> </u>  |          |          | Sele     | ect Device Type: | QDD Hos    | t 👻 US   | B instance: |          | •        | Module Found    |

| ~     |      |           | N 4 -      |        | ~      | V                | 1         | c        | 12.54    |          | Initialize       | Refr       | esh      | Pause Mo    | onitor   | About Us | Module Not Four |

| Lon   | nm   | on        |            |        |        |                  |           | erface   | e Kit    |          |                  |            |          |             |          |          | USB Error       |

|       |      |           | C          | IMIS   | Versi  | on: 3.           | 0         |          |          |          |                  |            |          |             |          |          |                 |

|       |      |           |            | Swite  | h to C | MIS 4.0          |           |          |          |          |                  |            |          |             |          |          |                 |

| nitor |      |           |            |        |        |                  |           |          |          |          |                  |            |          |             |          |          |                 |

|       | Modu | ıle Monit | or         |        |        |                  |           | Interrup | t Flags  |          |                  |            |          |             |          |          |                 |

|       | Ch   | RX LOS    | TX LOS     | RX LOL | TX LOL | TX Fault         | State Cng | Alarms   |          |          |                  | Warnin     | gs       |             |          |          |                 |

|       | 1    |           |            |        |        |                  |           |          | RX Power |          | TX Power         |            | RX Power |             | TX Power | C        | State Changed   |

|       | 2    |           |            |        |        |                  |           | Ch<br>1  | High Low | High Low | High Low         | Ch<br>1    | High Low | High Low    | High Low |          |                 |

|       | 3    |           |            |        |        |                  |           | 2        |          |          |                  | 2          |          |             |          |          |                 |

|       | 4    |           |            |        |        |                  |           | 3        |          |          |                  | 3          |          |             |          |          |                 |

|       | 6    |           |            |        |        |                  |           | 4        |          |          |                  | 4          |          |             |          |          |                 |

|       | 7    |           |            |        |        |                  |           | 5        |          |          |                  | 5          |          |             |          |          |                 |

|       | 8    |           |            |        |        |                  |           | 6        |          |          |                  | 6          |          |             |          |          |                 |

|       |      |           |            |        |        |                  |           | 8        |          |          |                  | 8          |          |             |          |          |                 |

|       | Chan | inels Mor | itor<br>Od | Rm     | () r   | nW               | _         |          | High Lov | N        | High Low         |            | High Lo  | w           | High Low |          |                 |

|       | Ch   | RX I      | Power      | тх в   | -      | TX Pow           | er        | Temp     |          | AUX 1    |                  | Temp       |          | AUX 1       |          |          |                 |

|       | 1    |           |            |        |        |                  |           | VCC 3    | .3 () () | AUX 2    |                  | VCC 3      | .3 () (  | AUX 2       |          |          |                 |

|       | 2    |           |            |        |        |                  |           | Vendor   | Def 🔿 🔿  | AUX 3    |                  | Vendor     | Def      | AUX 3       |          |          |                 |

|       | 3    |           |            |        |        |                  |           | Module / | Nonitor  |          |                  |            |          | MCB VCC N   | Nonitor  | MCB C    | urrent Monitor  |

|       | 4    |           |            |        |        |                  |           | Temp     |          | A        | UX1(TEC currer   | nt)        |          | VCC:        |          | Curren   | nt VCC:         |

|       | 5    |           |            |        |        |                  |           | Supply   | 3.3V     | A        | UX2(TEC currer   | nt)        |          | VCC1:       |          | Curren   | t VCCTX:        |

|       | 6    |           |            |        |        |                  |           |          |          | A        | UX3(Laser Temp   | <b>)</b> ( |          | (Only for   | QDD-MXP) | Curren   | nt VCCRX:       |

|       | 7    |           |            |        |        |                  |           |          |          |          |                  |            |          | VCCTX:      |          |          |                 |

Figure 2: GUI Window

7

#### 2. CMIS Version

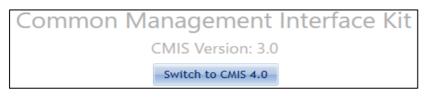

The GUI covers the CMIS 3.0 and CMIS 4.0. The user must choose the CMIS version first.

Figure 3: CMIS Version Selection

By clicking on the button shown above, the user can switch between CMIS 3.0 and CMIS 4.0. Depending on the CMIS Version chosen by the user, the list of devices will change. Below is a summary of supported hosts based on CMIS version.

- CMIS Version 3.0

- o QDD Host

- o OSFP Hosts (ML4064-TR is under the OSFP family)

- CMIS Version 4.0

- QDD Hosts (ML4062-TR is under the QDD family)

- OSFP Hosts (ML4064-TR is under the OSFP family)

- o QSFP Host

- o SFP-DD Host

- o DSFP Host

#### 3. Communication

The communication between the GUI and the host is established from the Communication window. Under this window, the user can select the Device Type and the USB instance.

The connection is established by clicking the Initialize button. This button is the application main entry point. Once a USB connection is established, the Host checks if a Module is inserted, and accordingly illuminates the corresponding (Module Found or Module Not Found) LED. If a Module is inserted, the initialization process proceeds with checking the related Hardware pins to ensure that the module is selected and ready to communicate with host.

Also, the following buttons are available in the Communication window.

Refresh button: Checks for connection status, refresh Hardware Readings and updates GUI. Pause Monitor button: Pause/Resume monitoring.

About Us button: Shows software information (name, version) and company information.

| Select Device Type | QDD Host - | USB instance: |          | Module Found  |

|--------------------|------------|---------------|----------|---------------|

| Initialize         | Refresh    | Pause Monitor | About Us | USB Connected |

|                    |            |               |          | USB Error     |

|                    |            |               |          |               |

Figure 2: Communication Tab

#### 4. GUI Sections

The ML-CMIS GUI contains the following tabs:

- Monitor

- Interrupt Masks

- Controls

- Low Speed Signals

- Identification

- Options Available

- Load/Save MSA

- Load/Save Page 10/11h

- I2C R/W

- I2C R/W Advanced

- DVT

- QDD-MXP (only for QSFP-DD Host)

All these tabs are common for all hosts. The subsequent sections will cover each tab separately. Any difference between various hosts in a specific tab will be mentioned explicitly.

#### 4.1 Monitor

The Monitor tab shows the digital diagnostic monitoring flags status.

All alarms and warnings are expressed with LEDs as shown in Figure 5, when a flag is asserted, the corresponding LED turns ON (becomes red), when not asserted the LED remains transparent.

Also, the Monitor tab shows measurements of various monitoring values (voltage, current and temperature) and are displayed continuously.

Two main measurements windows are available:

- 1 Module Monitor

- 2 MCB Monitor

Note that the measured quantities differ from MCB to another depending on the implementation.

| Mod  | ule Monitor   |           |        |          |           | Interrupt | Flags    |          |               |        |          |           |          |         |              |

|------|---------------|-----------|--------|----------|-----------|-----------|----------|----------|---------------|--------|----------|-----------|----------|---------|--------------|

| Ch   | RX LOS TX I   | OS RX LOI | TX LOL | TX Fault | State Cng | Alarms    |          |          |               | Warnin | ps       |           |          |         |              |

| 1    |               |           |        |          |           |           | RX Power | TX Bias  | TX Power      |        | RX Power | TX Bias   | TX Power | 0       | State Change |

| 2    |               |           |        |          |           | Ch        | High Low | High Low | High Low      | Ch     | High Low | High Low  | High Low |         |              |

| 3    |               |           |        |          |           | 1         |          |          |               | 1      |          |           |          |         |              |

| 4    |               |           |        |          |           | 2         |          |          |               | 2      |          |           |          |         |              |

| 1000 |               |           |        |          |           | 3         |          |          |               | 3      |          |           |          |         |              |

| 5    |               |           |        |          |           | 4         |          |          |               | 4      |          |           |          |         |              |

| 6    |               |           |        |          |           | 5         |          |          |               | 5      |          |           |          |         |              |

| 7    |               |           |        |          |           | 6         |          |          |               | 6      |          |           |          |         |              |

| 8    |               |           |        |          |           | 7         |          |          |               | 7      |          |           |          |         |              |

|      |               |           |        |          |           | 8         |          |          |               | 8      |          |           |          |         |              |

| Cha  | nnels Monitor |           |        |          |           |           |          |          |               |        |          |           |          |         |              |

|      | C             | dBm       | •      |          |           |           | High Lov |          | ligh Low      |        | High Lo  |           | High Low |         |              |

| Ch   | RX Pow        | er TX     | Bias   | TX Powe  | er        | Temp      |          |          |               | Temp   |          |           |          |         |              |

| 1    |               |           |        |          |           | VCC 3.    | .3 O C   | AUX 2    |               | VCC 3  | 3 0 0    | AUX 2     |          |         |              |

| 2    |               |           |        |          |           | Vendor    | Def 🔿 🔿  | AUX 3    |               | Vendor | Def 🔿 🤇  | AUX 3     |          |         |              |

| 3    |               |           |        |          |           | Module A  | lonitor  |          |               |        | 11       | MCB VCC / | Nonitor  | MCB Cur | rent Monitor |

| 4    |               |           |        |          |           | Temp      |          | AL       | JX1(TEC curre | nt)    |          | VCC:      |          | Current | VCC:         |

| 5    |               |           |        |          |           | Supply    | 3.3V     | AU       | X2(TEC curre  | nt)    |          | VCC1:     |          | Current | VCCTX:       |

| 6    |               |           |        |          |           |           |          |          | JX3(Laser Tem |        |          |           | QDD-MXP) |         |              |

| 7    |               |           |        |          |           |           |          |          | marcador rom  |        |          | VCCTX:    |          | Current | Activat      |

|      |               |           |        |          |           |           |          |          |               |        |          | VCCIA:    |          |         | Go to Set    |

Figure 5: Monitor Tab

The following table shows the MSA memory mapping for the monitoring tab objects.

| Byte | Bit | Name                                    | Description                                                                                                                                                                                                                                                | Туре       |

|------|-----|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 14   | 7-  | 0 Module Monitor 1:<br>Temperature MSB  | Internally measured temperature: signed 2's<br>complement in 1/256 degree Celsius increments<br>NOTE: Temp can be below 0.                                                                                                                                 | RO<br>Opt. |

| 15   | 7-  | 0 Module Monitor 1:<br>Temperature1 LSB |                                                                                                                                                                                                                                                            |            |

| 16   | 7-  |                                         | Internally measured 3.3 volt input supply voltage: in 100 µV increments                                                                                                                                                                                    | RO<br>Opt. |

| 17   | 7-  |                                         |                                                                                                                                                                                                                                                            |            |

| 18   | 7-  |                                         | TEC Current or Reserved monitor<br>TEC Current: signed 2's complement in 1/32767%                                                                                                                                                                          | RO<br>Opt. |

| 19   | 7-  | 0 Module Monitor 3: Aux 1<br>LSB        | increments of maximum TEC current<br>+32767 is max TEC current (100%) – Max Heating<br>-32767 is min TEC current (100%) – Max Cooling                                                                                                                      |            |

| 20   | 7-  | 0 Module Monitor 4: Aux 2<br>MSB        | TEC Current or Laser Temperature monitor TEC Current:<br>signed 2's complement in 1/32767% increments of                                                                                                                                                   | RO<br>Opt. |

| 21   | 7-  | 0 Module Monitor 4: Aux 2<br>LSB        | maximum TEC current<br>+32767 is max TEC current (100%) – Max Heating<br>-32767 is min TEC current (100%) – Max Cooling<br>Laser Temperature: signed 2's complement in 1/256<br>degree Celsius increments<br>See Page 01h Byte 145 Table Table 8-30        |            |

| 22   | 7-  | MSB                                     | Laser Temperature or additional supply voltage monitor<br>Laser Temperature: signed 2's complement in 1/256<br>degree Celsius increments                                                                                                                   | RO<br>Opt. |

| 20   |     | LSB                                     | Additional supply voltage monitor: in 100 µV increments<br>See Page 01h Byte 145 Table Table 8-30                                                                                                                                                          |            |

| 24   | 7-  | MSB                                     | Custom monitor                                                                                                                                                                                                                                             | RO<br>Opt. |

| 25   | 7-  | LSB                                     |                                                                                                                                                                                                                                                            |            |

| 8    | 7   | L-CDB block 2 complete                  | Latched flag to indicate completion of the CDB command for CDB block 2. Clear on Read (See Page 01h, Byte 163 bit 7)                                                                                                                                       | RO Opt.    |

|      | 6   | L-CDB block 1 complete                  | Latched flag to indicate completion of the CDB command for CDB block 1. Clear on Read (See Page 01h, Byte 163 bit 6)                                                                                                                                       | RO Opt.    |

|      | 5-3 | Reserved                                |                                                                                                                                                                                                                                                            | RQD        |

| -    | 2   | Data Path firmware fault                | Some modules may contain an auxiliary device for<br>processing the transmitted and received signals (e.g. a<br>DSP). The Data Path Firmware Fault flag becomes set when<br>an integrity check of the firmware for this auxiliary device<br>finds an error. | RO Opt.    |

|      | 1   | Module firmware fault                   | The Module Firmware Fault flag becomes set when an integrity check of the module firmware finds an error. There are several possible causes of the error such as program memory becoming corrupted and incomplete firmware loading.                        | RO<br>Opt. |

|      | 0   | L-Module state changed flag             | Latched Indication of change of Module state (see Table<br>8-5) Clear on Read                                                                                                                                                                              | RO RQD     |

| 9    | 7   | L-Vcc3.3v Low Warning                   | Latched low 3.3 volts supply voltage warning flag. Clear on<br>Read                                                                                                                                                                                        | RO Opt.    |

|      | 6   | L-Vcc3.3v High Warning                  | Latched high 3.3 volts supply voltage warning flag. Clear on Read                                                                                                                                                                                          |            |

|      | 5   | L-Vcc3.3v Low Alarm                     | Latched low 3.3 volts supply voltage alarm flag. Clear on Read                                                                                                                                                                                             |            |

|      | 4   | L-Vcc3.3v High Alarm                    | Latched high 3.3 volts supply voltage alarm flag. Clear on Read                                                                                                                                                                                            |            |

| ŀ    | 3   | L-Temp Low Warning                      | Latched low temperature warning flag. Clear on Read                                                                                                                                                                                                        | 1          |

|      | 2   | L-Temp High Warning                     | Latched high temperature warning flag. Clear on Read                                                                                                                                                                                                       | -          |

| Γ    | ~   |                                         |                                                                                                                                                                                                                                                            |            |

|      | 1   | L-Temp Low Alarm                        | Latched low temperature alarm flag. Clear on Read                                                                                                                                                                                                          |            |

|   |      | ан I | 210                                            |                                                                |               |

|---|------|------|------------------------------------------------|----------------------------------------------------------------|---------------|

| m | ull  |      | ane                                            |                                                                |               |

| г |      | _    |                                                |                                                                |               |

|   | 10   | 7    | L-Aux 2 Low Warning                            | Latched low warning for Aux 2 monitor. Clear on Read           | RO            |

|   |      | 6    | L-Aux 2 High Warning                           | Latched high warning for Aux 2 monitor. Clear on Read          | Opt.          |

|   |      | 5    | L-Aux 2 Low Alarm                              | Latched low alarm for Aux 2 monitor. Clear on Read             | -             |

|   |      | 4    | L-Aux 2 High Alarm                             | Latched high alarm for Aux 2 monitor. Clear on Read            | -             |

|   |      | 3    | L-Aux 1 Low Warning                            | Latched low warning for Aux 1 monitor. Clear on Read           | -             |

|   |      | 2    | L-Aux 1 High Warning                           | Latched high warning for Aux 1 monitor. Clear on Read          | -             |

|   |      | 1    | L-Aux 1 Low Alarm                              | Latched low alarm for Aux 1 monitor. Clear on Read             | -             |

| - |      | 0    | L-Aux 1 High Alarm                             | Latched high alarm for Aux 1 monitor. Clear on Read            |               |

|   | 11   | 7    | L-Vendor Defined Low Warning                   | Latched low warning for Vendor Defined Monitor. Clear on Read  | RO<br>Opt.    |

|   |      | 6    | L-Vendor Defined High Warning                  | Latched high warning for Vendor Defined Monitor. Clear on Read |               |

|   |      | 5    | L-Vendor Defined Low Alarm                     | Latched low alarm for Vendor Defined Monitor. Clear on Read    |               |

|   |      | 4    | L-Vendor Defined High Alarm                    | Latched high alarm for Vendor Defined Monitor. Clear on Read   |               |

|   |      | 3    | L-Aux 3 Low Warning                            | Latched low warning for Aux 3 monitor. Clear on Read           |               |

|   |      | 2    | L-Aux 3 High Warning                           | Latched high warning for Aux 3 monitor. Clear on Read          |               |

|   |      | 1    | L-Aux 3 Low Alarm                              | Latched low alarm for Aux 3 monitor. Clear on Read             |               |

|   |      | 0    | L-Aux 3 High Alarm                             | Latched high alarm for Aux 3 monitor. Clear on Read            |               |

|   | 12   | 7-0  | Reserved                                       |                                                                |               |

|   | 13   | 7-0  | Custom                                         |                                                                |               |

|   | Byte | Bit  | Name                                           | Description                                                    | Туре          |

|   | 134  | 7    | L-Data Path State Changed<br>flag, host lane 8 | Latched Data Path State Changed flag for host lane 8           | RO/COR<br>RQD |

|   |      | 6    | L-Data Path State changed<br>flag, host lane 7 | Latched Data Path State Changed flag for host lane 7           |               |

|   |      | 5    | L-Data Path State Changed<br>flag, host lane 6 | Latched Data Path State Changed flag for host lane 6           |               |

|   |      | 4    | L-Data Path State Changed<br>flag, host lane 5 | Latched Data Path State Changed flag for host lane 5           |               |

|   |      | 3    | L-Data Path State Changed<br>flag, host lane 4 | Latched Data Path State Changed flag for host lane 4           |               |

|   |      | 2    | L-Data Path State Changed<br>flag, host lane 3 | Latched Data Path State Changed flag for host lane 3           |               |

|   |      | 1    | L-Data Path State Changed<br>flag, host lane 2 | Latched Data Path State Changed flag for host lane 2           |               |

|   |      | 0    | L-Data Path State Changed<br>flag, host lane 1 | Latched Data Path State Changed flag for host lane 1           |               |

| Γ | 135  | 7    | L-Tx8 Fault flag                               | Latched Tx Fault flag, media lane 8                            | RO            |

|   |      | 6    | L-Tx7 Fault flag                               | Latched Tx Fault flag, media lane 7                            | Opt.          |

|   |      | 5    | L-Tx6 Fault flag                               | Latched Tx Fault flag, media lane 6                            |               |

|   |      | 4    | L-Tx5 Fault flag                               | Latched Tx Fault flag, media lane 5                            |               |

|   |      | 3    | L-Tx4 Fault flag                               | Latched Tx Fault flag, media lane 4                            |               |

|   |      | 2    | L-Tx3 Fault flag                               | Latched Tx Fault flag, media lane 3                            |               |

|   |      | 1    | L-Tx2 Fault flag                               | Latched Tx Fault flag, media lane 2                            |               |

|   |      | 0    | L-Tx1 Fault flag                               | Latched Tx Fault flag, media lane 1                            |               |

|   | 136  | 7    | L-Tx8 LOS flag                                 | Latched Tx LOS flag, lane 8                                    | RO            |

|   |      | 6    | L-Tx7 LOS flag                                 | Latched Tx LOS flag, lane 7                                    | Opt.          |

|   |      | 5    | L-Tx6 LOS flag                                 | Latched Tx LOS flag, lane 6                                    |               |

|   |      | 4    | L-Tx5 LOS flag                                 | Latched Tx LOS flag, lane 5                                    |               |

|   |      | 3    | L-Tx4 LOS flag                                 | Latched Tx LOS flag, lane 4                                    |               |

|   |      | 2    | L-Tx3 LOS flag                                 | Latched Tx LOS flag, lane 3                                    |               |

|   |      | 1    | L-Tx2 LOS flag                                 | Latched Tx LOS flag, lane 2                                    |               |

|   |      | 0    | L-Tx1 LOS flag                                 | Latched Tx LOS flag, lane 1                                    |               |

|   | 137  | 7    | L-Tx8 CDR LOL flag                             | Latched Tx CDR LOL flag, lane 8. Clear on Read                 | RO            |

| mu | ltiL | ane                                              |                                                                                                                    |                  |

|----|------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------|

| 1  |      |                                                  |                                                                                                                    |                  |

|    | 6    | L-Tx7 CDR LOL flag                               | Latched Tx CDR LOL flag, lane 7. Clear on Read                                                                     | Opt.             |

|    | 5    | L-Tx6 CDR LOL flag                               | Latched Tx CDR LOL flag, lane 6. Clear on Read                                                                     | -                |

|    | 4    | L-Tx5 CDR LOL flag                               | Latched Tx CDR LOL flag, lane 5. Clear on Read                                                                     | -                |

|    | 3    | L-Tx4 CDR LOL flag                               | Latched Tx CDR LOL flag, lane 4. Clear on Read                                                                     |                  |

|    | 2    | L-Tx3 CDR LOL flag                               | Latched Tx CDR LOL flag, lane 3. Clear on Read                                                                     |                  |

|    | 1    | L-Tx2 CDR LOL flag                               | Latched Tx CDR LOL flag, lane 2. Clear on Read                                                                     |                  |

|    | 0    | L-Tx1 CDR LOL flag                               | Latched Tx CDR LOL flag, lane 1. Clear on Read                                                                     |                  |

| 13 | 38 7 | L-Tx8 Adaptive Input Eq Fault<br>Lane 8 flag     | Latched Tx Adaptive Input Eq. Fault Lane 8. Clear on Read                                                          | RO<br>Opt.       |

|    | 6    | L-Tx7 Adaptive Input Eq Fault<br>Lane 7 flag     | Latched Tx Adaptive Input Eq. Fault Lane 7. Clear on Read                                                          |                  |

|    | 5    | L-Tx6 Adaptive Input Eq Fault<br>Lane 6 flag     | Latched Tx Adaptive Input Eq. Fault Lane 6. Clear on Read                                                          |                  |

|    | 4    | L-Tx5 Adaptive Input Eq Fault<br>Lane 5 flag     | Latched Tx Adaptive Input Eq. Fault Lane 5. Clear on Read                                                          |                  |

|    | 3    | L-Tx4 Adaptive Input Eq Fault<br>Lane 4 flag     | Latched Tx Adaptive Input Eq. Fault Lane 4. Clear on Read                                                          |                  |

|    | 2    | L-Tx3 Adaptive Input Eq Fault<br>Lane 3 flag     | Latched Tx Adaptive Input Eq. Fault Lane 3. Clear on Read                                                          |                  |

|    | 1    | L-Tx2 Adaptive Input Eq Fault<br>Lane 2 flag     | Latched Tx Adaptive Input Eq. Fault Lane 2. Clear on Read                                                          | -                |

|    | 0    | L-Tx1 Adaptive Input Eq Fault<br>Lane 1 flag     | Latched Tx Adaptive Input Eq. Fault Lane 1. Clear on Read                                                          |                  |

| 13 | 39 7 | L-Tx8 Power High alarm                           | Tx output power High Alarm, media lane 8. Clear on Read                                                            | RO               |

|    | 6    | L-Tx7 Power High alarm                           | Tx output power High Alarm, media lane 7. Clear on Read                                                            | Opt.             |

|    | 5    | L-Tx6 Power High alarm<br>L-Tx5 Power High alarm | Tx output power High Alarm, media lane 6. Clear on Read<br>Tx output power High Alarm, media lane 5. Clear on Read | -                |

|    | 3    | L-Tx4 Power High alarm                           | Tx output power High Alarm, media lane 3. Clear on Read                                                            |                  |

|    | 2    | L-Tx3 Power High alarm                           | Tx output power High Alarm, media lane 3. Clear on Read                                                            |                  |

|    | 1    | L-Tx2 Power High alarm                           | Tx output power High Alarm, media lane 2. Clear on Read                                                            |                  |

|    | 0    | L-Tx1 Power High alarm                           | Tx output power High Alarm, media lane 1. Clear on Read                                                            |                  |

| 14 |      | L-Tx8 Power Low alarm                            | Tx output power Low alarm, media lane 8. Clear on Read                                                             | RO               |

|    | 6    | L-Tx7 Power Low alarm                            | Tx output power Low alarm, media lane 7. Clear on Read                                                             | Opt.             |

|    | 5    | L-Tx6 Power Low alarm                            | Tx output power Low alarm, media lane 6. Clear on Read                                                             | -                |

|    | 4    | L-Tx5 Power Low alarm                            | Tx output power Low alarm, media lane 5. Clear on Read                                                             | -                |

|    | 3    | L-Tx4 Power Low alarm                            | Tx output power Low alarm, media lane 4. Clear on Read                                                             | -                |

|    | 2    | L-Tx3 Power Low alarm<br>L-Tx2 Power Low alarm   | Tx output power Low alarm, media lane 3. Clear on Read<br>Tx output power Low alarm, media lane 2. Clear on Read   | -                |

|    | 0    | L-Tx1 Power Low alarm                            | Tx output power Low alarm, media lane 2. Clear on Read                                                             | -                |

| 14 |      | L-Tx8 Power High warning                         | Tx output power High warning, media lane 1. Clear on Read                                                          | RO               |

| 1  | 6    | L-Tx7 Power High warning                         | Tx output power High warning, media lane 0. Clear on Read                                                          | Opt.             |

|    | 5    | L-Tx6 Power High warning                         | Tx output power High warning, media lane 6. Clear on Read                                                          | opti             |

|    | 4    | L-Tx5 Power High warning                         | Tx output power High warning, media lane 5. Clear on Read                                                          | 1                |

|    | 3    | L-Tx4 Power High warning                         | Tx output power High warning, media lane 4. Clear on Read                                                          |                  |

|    | 2    | L-Tx3 Power High warning                         | Tx output power High warning, media lane 3. Clear on Read                                                          | te Windov        |

|    | 1    | L-Tx2 Power High warning                         | Tx output power High warning, media lane 2. Clear on Readse                                                        | ettings to activ |

|    | 0    | L-Tx1 Power High warning                         | Tx output power High warning, media lane 1. Clear on Read                                                          |                  |

| 14 | 12 7 | L-Tx8 Power Low warning                          | Tx output power Low warning, media lane 8. Clear on Read                                                           | RO               |

|    | 6    | L-Tx7 Power Low warning                          | Tx output power Low warning, media lane 7. Clear on Read                                                           | Opt.             |

|    | 5    | L-Tx6 Power Low warning                          | Tx output power Low warning, media lane 6. Clear on Read                                                           |                  |

|    | 4    | L-Tx5 Power Low warning                          | Tx output power Low warning, media lane 5. Clear on Read                                                           |                  |

| m | ult | iĻ | ane                     |                                                          |      |

|---|-----|----|-------------------------|----------------------------------------------------------|------|

| _ |     |    |                         |                                                          |      |

|   |     | 3  | L-Tx4 Power Low warning | Tx output power Low warning, media lane 4. Clear on Read |      |

|   |     | 2  | L-Tx3 Power Low warning | Tx output power Low warning, media lane 3. Clear on Read |      |

|   |     | 1  | L-Tx2 Power Low warning | Tx output power Low warning, media lane 2. Clear on Read |      |

|   |     | 0  | L-Tx1 Power Low warning | Tx output power Low warning, media lane 1. Clear on Read |      |

|   | 143 | 7  | L-Tx8 Bias High Alarm   | Tx Bias High Alarm, media lane 8. Clear on Read          | RO   |

|   |     | 6  | L-Tx7 Bias High Alarm   | Tx Bias High Alarm, media lane 7. Clear on Read          | Opt. |

|   |     | 5  | L-Tx6 Bias High Alarm   | Tx Bias High Alarm, media lane 6. Clear on Read          |      |

|   |     | 4  | L-Tx5 Bias High Alarm   | Tx Bias High Alarm, media lane 5. Clear on Read          |      |

|   |     | 3  | L-Tx4 Bias High Alarm   | Tx Bias High Alarm, media lane 4. Clear on Read          |      |

|   |     | 2  | L-Tx3 Bias High Alarm   | Tx Bias High Alarm, media lane 3. Clear on Read          |      |

|   |     | 1  | L-Tx2 Bias High Alarm   | Tx Bias High Alarm, media lane 2. Clear on Read          |      |

|   |     | 0  | L-Tx1 Bias High Alarm   | Tx Bias High Alarm, media lane 1. Clear on Read          |      |

|   | 144 | 7  | L-Tx8 Bias Low alarm    | Tx Bias Low alarm, media lane 8. Clear on Read           | RO   |

|   |     | 6  | L-Tx7 Bias Low alarm    | Tx Bias Low alarm, media lane 7. Clear on Read           | Opt. |

|   |     | 5  | L-Tx6 Bias Low alarm    | Tx Bias Low alarm, media lane 6. Clear on Read           |      |

|   |     | 4  | L-Tx5 Bias Low alarm    | Tx Bias Low alarm, media lane 5. Clear on Read           |      |

|   |     | 3  | L-Tx4 Bias Low alarm    | Tx Bias Low alarm, media lane 4. Clear on Read           |      |

|   |     | 2  | L-Tx3 Bias Low alarm    | Tx Bias Low alarm, media lane 3. Clear on Read           |      |

|   |     | 1  | L-Tx2 Bias Low alarm    | Tx Bias Low alarm, media lane 2. Clear on Read           |      |

|   |     | 0  | L-Tx1 Bias Low alarm    | Tx Bias Low alarm, media lane 1. Clear on Read           |      |

|   | 145 | 7  | L-Tx8 Bias High warning | Tx Bias High warning, media lane 8. Clear on Read        | RO   |

|   |     | 6  | L-Tx7 Bias High warning | Tx Bias High warning, media lane 7. Clear on Read        | Opt. |

|   |     | 5  | L-Tx6 Bias High warning | Tx Bias High warning, media lane 6. Clear on Read        |      |

|   |     | 4  | L-Tx5 Bias High warning | Tx Bias High warning, media lane 5. Clear on Read        |      |

|   |     | 3  | L-Tx4 Bias High warning | Tx Bias High warning, media lane 4. Clear on Read        |      |

|   |     | 2  | L-Tx3 Bias High warning | Tx Bias High warning, media lane 3. Clear on Read        |      |

|   |     | 1  | L-Tx2 Bias High warning | Tx Bias High warning, media lane 2. Clear on Read        |      |

|   |     | 0  | L-Tx1 Bias High warning | Tx Bias High warning, media lane 1. Clear on Read        |      |

|   | 146 | 7  | L-Tx8 Bias Low warning  | Tx Bias Low warning, media lane 8. Clear on Read         | RO   |

|   |     | 6  | L-Tx7 Bias Low warning  | Tx Bias Low warning, media lane 7. Clear on Read         | Opt. |

|   |     | 5  | L-Tx6 Bias Low warning  | Tx Bias Low warning, media lane 6. Clear on Read         |      |

|   |     | 4  | L-Tx5 Bias Low warning  | Tx Bias Low warning, media lane 5. Clear on Read         |      |

|   |     | 3  | L-Tx4 Bias Low warning  | Tx Bias Low warning, media lane 4. Clear on Read         |      |

|   |     | 2  | L-Tx3 Bias Low warning  | Tx Bias Low warning, media lane 3. Clear on Read         |      |

|   |     | 1  | L-Tx2 Bias Low warning  | Tx Bias Low warning, media lane 2. Clear on Read         |      |

|   |     | 0  | L-Tx1 Bias Low warning  | Tx Bias Low warning, media lane 1. Clear on Read         |      |

|   | 147 | 7  | L-Rx8 LOS               | Latched Rx LOS flag, media lane 8. Clear on Read         | RO   |

|   |     | 6  | L-Rx7 LOS               | Latched Rx LOS flag, media lane 7. Clear on Read         | Opt. |

|   |     | 5  | L-Rx6 LOS               | Latched Rx LOS flag, media lane 6. Clear on Read         | 7    |

|   |     | 4  | L-Rx5 LOS               | Latched Rx LOS flag, media lane 5. Clear on Read         | 1    |

|   |     | 3  | L-Rx4 LOS               | Latched Rx LOS flag, media lane 4. Clear on Read         | 7    |

|   |     | 2  | L-Rx3 LOS               | Latched Rx LOS flag, media lane 3. Clear on Read         | 7    |

|   |     | 1  | L-Rx2 LOS               | Latched Rx LOS flag, media lane 2. Clear on Read         | 1    |

|   |     | 0  | L-Rx1 LOS               | Latched Rx LOS flag, media lane 1. Clear on Read         | 1    |

| ŀ | 148 | 7  | L-Rx8 CDR LOL           | Latched Rx CDR LOL flag, media lane 8. Clear on Read     | RO   |

|   |     | 6  | L-Rx7 CDR LOL           | Latched Rx CDR LOL flag, media lane 7. Clear on Read     | Opt. |

|   |     | 5  | L-Rx6 CDR LOL           | Latched Rx CDR LOL flag, media lane 6. Clear on Read     |      |

|   |     | 4  | L-Rx5 CDR LOL           | Latched Rx CDR LOL flag, media lane 5. Clear on Read     | 1    |

|   |     | 3  | L-Rx4 CDR LOL           | Latched Rx CDR LOL flag, media lane 4. Clear on Read     | 1    |

| F |     |    |                         |                                                          | •    |

| multiLane |  |

|-----------|--|

|           |  |

| 1 1  | 2      | L-Rx3 CDR LOL         |           | Latched Rx CDR LOL flag, media lane 3. Clear on Read                                                                 |           |

|------|--------|-----------------------|-----------|----------------------------------------------------------------------------------------------------------------------|-----------|

|      | 1      | L-Rx2 CDR LOL         |           | Latched Rx CDR LOL flag, media lane 2. Clear on Read                                                                 |           |

|      | 0      | L-Rx1 CDR LOL         |           | Latched Rx CDR LOL flag, media lane 1. Clear on Read                                                                 |           |

| 149  | 7      | L-Rx8 Power High alar | m         | Rx input power High alarm, media lane 8. Clear on Read                                                               | RO        |

|      | 6      | L-Rx7 Power High alar |           | Rx input power High alarm, media lane 7. Clear on Read                                                               | Opt.      |

|      | 5      | L-Rx6 Power High alar |           | Rx input power High alarm, media lane 6. Clear on Read                                                               | opt.      |

|      | 4      | L-Rx5 Power High alar |           | Rx input power High alarm, media lane 5. Clear on Read                                                               |           |

|      | 3      | L-Rx4 Power High alar |           | Rx input power High alarm, media lane 4. Clear on Read                                                               |           |

|      | 2      | L-Rx3 Power High alar |           | Rx input power High alarm, media lane 3. Clear on Read                                                               |           |

|      | 1      | L-Rx2 Power High alar |           | Rx input power High alarm, media lane 3. Clear on Read                                                               |           |

|      | 0      | L-Rx1 Power High alar |           | Rx input power High alarm, media lane 1. Clear on Read                                                               |           |

| 150  | 7      | L-Rx8 Power Low alarn |           | Rx input power Low alarm, media lane 8. Clear on Read                                                                | RO        |

| 150  | 6      | L-Rx7 Power Low alarr |           | Rx input power Low alarm, media lane 7. Clear on Read                                                                | Opt.      |

|      | 5      | L-Rx6 Power Low alarn |           | Rx input power Low alarm, media lane 6. Clear on Read                                                                | opt.      |

|      | 4      | L-Rx5 Power Low alarr |           | Rx input power Low alarm, media lane 5. Clear on Read                                                                |           |

|      | 3      | L-Rx4 Power Low alarr |           | Rx input power Low alarm, media lane 4. Clear on Read                                                                |           |

|      | 2      | L-Rx3 Power Low alarr |           | Rx input power Low alarm, media lane 4. Clear on Read                                                                |           |

|      | 1      | L-Rx2 Power Low alarr |           | Rx input power Low alarm, media lane 5. Clear on Read                                                                |           |

|      | 0      | L-Rx1 Power Low alarr |           | Rx input power Low alarm, media lane 2. Clear on Read                                                                |           |

| 151  | 7      | L-Rx8 Power High war  |           |                                                                                                                      | RO        |

| 151  | 6      | L-Rx7 Power High war  |           | Rx input power High warning, media lane 8. Clear on Read                                                             | Opt.      |

|      | 5      | L-Rx6 Power High war  |           | Rx input power High warning, media lane 7. Clear on Read<br>Rx input power High warning, media lane 6. Clear on Read | Opt.      |

|      | 5<br>4 | L-Rx5 Power High war  |           | Rx input power High warning, media lane 5. Clear on Read                                                             |           |

|      |        |                       |           |                                                                                                                      |           |

|      | 3      | L-Rx4 Power High war  |           | Rx input power High warning, media lane 4. Clear on Read                                                             |           |

|      | 2      | L-Rx3 Power High war  |           | Rx input power High warning, media lane 3. Clear on Read                                                             |           |

| -    | 0      | L-Rx2 Power High war  |           | Rx input power High warning, media lane 2. Clear on Read                                                             |           |

| 150  | 7      | L-Rx1 Power High war  |           | Rx input power High warning, media lane 1. Clear on Read                                                             | <b>DO</b> |

| 152  |        | L-Rx8 Power Low warr  |           | Rx input power Low warning, media lane 8. Clear on Read                                                              | RO        |

|      | 6      | L-Rx7 Power Low warr  |           | Rx input power Low warning, media lane 7. Clear on Read                                                              | Opt.      |

|      | 5      | L-Rx6 Power Low warr  |           | Rx input power Low warning, media lane 6. Clear on Read                                                              |           |

|      | 4      | L-Rx5 Power Low warr  |           | Rx input power Low warning, media lane 5. Clear on Read                                                              |           |

|      | 3      | L-Rx4 Power Low warr  |           | Rx input power Low warning, media lane 4. Clear on Read                                                              |           |

|      | 2      | L-Rx3 Power Low warr  |           | Rx input power Low warning, media lane 3. Clear on Read                                                              |           |

| -    | 1      | L-Rx2 Power Low warr  |           | Rx input power Low warning, media lane 2. Clear on Read                                                              |           |

|      | 0      | L-Rx1 Power Low warr  |           | Rx input power Low warning, media lane 1. Clear on Read                                                              |           |

| Byte | Bit    | Name                  | Descripti | on                                                                                                                   | Туре      |

| 153  | 7-0    | Reserved              |           |                                                                                                                      | RO        |

| 154  | 7-0    | Tx1 Power MSB         |           | measured Tx output optical power: unsigned integer in 0.1                                                            | RO        |

| 155  | 7-0    | Tx1 Power LSB         |           | nents, yielding a total measurement range of 0 to 6.5535                                                             | Opt.      |

| 156  | 7-0    | Tx2 Power MSB         | mw (~-40  | ) to +8.2 dBm)                                                                                                       |           |

| 157  | 7-0    | Tx2 Power LSB         |           |                                                                                                                      |           |

| 158  | 7-0    | Tx3 Power MSB         |           |                                                                                                                      |           |

| 159  | 7-0    | Tx3 Power LSB         |           |                                                                                                                      |           |

| 160  | 7-0    | Tx4 Power MSB         |           |                                                                                                                      |           |

| 161  | 7-0    | Tx4 Power LSB         |           |                                                                                                                      |           |

| 162  | 7-0    | Tx5 Power MSB         |           |                                                                                                                      |           |

| 163  | 7-0    | Tx5 Power LSB         |           |                                                                                                                      |           |

| 164  | 7-0    | Tx6 Power MSB         |           |                                                                                                                      |           |

| 165  | 7-0    | Tx6 Power LSB         |           |                                                                                                                      |           |

| 166  | 7-0    | Tx7 Power MSB         |           |                                                                                                                      |           |

| 167  | 7-0    | Tx7 Power LSB         |           |                                                                                                                      |           |

| 168  | 7-0    | Tx8 Power MSB         |           |                                                                                                                      |           |

| 169  | 7-0    | Tx8 Power LSB         |           |                                                                                                                      |           |

| multiLane |  |

|-----------|--|

|-----------|--|

| 170 | 7-0 | Tx1 Bias MSB  | Internally measured Tx bias current monitor: unsigned integer in 2 uA | RO   |

|-----|-----|---------------|-----------------------------------------------------------------------|------|

| 171 | 7-0 | Tx1 Bias LSB  | increments, times the multiplier from Table 8-33.                     | Opt. |

| 172 | 7-0 | Tx2 Bias MSB  |                                                                       |      |

| 173 | 7-0 | Tx2 Bias LSB  |                                                                       |      |

| 174 | 7-0 | Tx3 Bias MSB  |                                                                       |      |

| 175 | 7-0 | Tx3 Bias LSB  |                                                                       |      |

| 176 | 7-0 | Tx4 Bias MSB  |                                                                       |      |

| 177 | 7-0 | Tx4 Bias LSB  |                                                                       |      |

| 178 | 7-0 | Tx5 Bias MSB  |                                                                       |      |

| 179 | 7-0 | Tx5 Bias LSB  |                                                                       |      |

| 180 | 7-0 | Tx6 Bias MSB  |                                                                       |      |

| 181 | 7-0 | Tx6 Bias LSB  |                                                                       |      |

| 182 | 7-0 | Tx7 Bias MSB  |                                                                       |      |

| 183 | 7-0 | Tx7 Bias LSB  |                                                                       |      |

| 184 | 7-0 | Tx8 Bias MSB  |                                                                       |      |

| 185 | 7-0 | Tx8 Bias LSB  |                                                                       |      |

| 186 | 7-0 | Rx1 Power MSB | Internally measured Rx input optical power:                           | RO   |

| 187 | 7-0 | Rx1 Power LSB | unsigned integer in 0.1 uW increments, yielding a total measurement   | Opt. |

| 188 | 7-0 | Rx2 Power MSB | range of 0 to 6.5535 mW (~-40 to +8.2 dBm)                            |      |

| 189 | 7-0 | Rx2 Power LSB |                                                                       |      |

| 190 | 7-0 | Rx3 Power MSB |                                                                       |      |

| 191 | 7-0 | Rx3 Power LSB |                                                                       |      |

| 192 | 7-0 | Rx4 Power MSB |                                                                       |      |

| 193 | 7-0 | Rx4 Power LSB |                                                                       |      |

| 194 | 7-0 | Rx5 Power MSB |                                                                       |      |

| 195 | 7-0 | Rx5 Power LSB |                                                                       |      |

| 196 | 7-0 | Rx6 Power MSB |                                                                       |      |

| 197 | 7-0 | Rx6 Power LSB |                                                                       |      |

| 198 | 7-0 | Rx7 Power MSB |                                                                       |      |

| 199 | 7-0 | Rx7 Power LSB |                                                                       |      |

| 200 | 7-0 | Rx8 Power MSB |                                                                       |      |

| 201 | 7-0 | Rx8 Power LSB |                                                                       |      |

#### 4.2 Interrupt Masks

Masks shown in this tab are used to prevent a specified flag of generating an interrupt (IntL) when asserted and prevent continued interruption from on-going conditions.

When a mask is set, an interrupt will not be asserted by the corresponding (Alarm/Warning) latched flag bit.

All Masking bits are volatile and will be reset (set to 0) on module startup.

|          | · ·       | this pag | e      | Refr    | resh —       | Alarm | -    | s       |       |      |        |    |     |                |        |     |     |     |       |  |

|----------|-----------|----------|--------|---------|--------------|-------|------|---------|-------|------|--------|----|-----|----------------|--------|-----|-----|-----|-------|--|

|          | e Chang   |          |        |         |              | Alan  |      | ower    | TX Bi |      | TX Pow |    | Wan | nings<br>RX Po |        | TXI |     | TVI | Power |  |

| Lane-Spe | cific Fla | g Masks  |        | _       |              |       | High |         | High  |      | High L |    | Ch  | High           |        |     | Low |     | Low   |  |

| Ch RX LC | S TX LO   | S RX LOL | TX LOL | TX Faul | t State Chng | 1     | mgn  | Eow I   | mgn   | m    | -      |    | 1   | mgn            | Elow I | mgn | EOW | mgn |       |  |

| 1 🔳      |           |          |        |         |              | 2     |      |         |       |      |        |    | 2   |                |        |     |     |     |       |  |

| 2        |           |          |        |         |              | 3     |      |         |       |      |        |    | 3   |                |        |     |     |     |       |  |

| 3        |           |          |        |         |              | 4     |      |         |       |      |        |    | 4   |                |        |     |     |     |       |  |

| 4 🔳      |           |          |        |         |              |       |      |         |       |      |        |    |     |                |        |     |     |     |       |  |

| 5        |           |          |        |         | E            | 5     |      |         |       |      |        |    | 5   |                |        |     | _   |     |       |  |

| 6        |           |          |        |         |              | 6     |      |         |       |      |        |    | 6   |                |        |     |     |     |       |  |

| 7        |           |          |        |         |              | 7     |      |         |       |      |        |    | 7   |                |        |     |     |     |       |  |

| 8        |           |          |        |         |              | 8     |      |         |       |      |        |    | 8   |                |        |     |     |     |       |  |

|          |           | -        |        |         |              |       | ÷    | ligh Lo | ow    |      | High L | ow |     | н              | igh I  | Low |     |     |       |  |

|          |           |          |        |         |              | Ten   |      |         |       | JX 2 |        |    | То  | mp             |        |     | AUX | 2   |       |  |

Figure 3: Interrupt Masks Tab

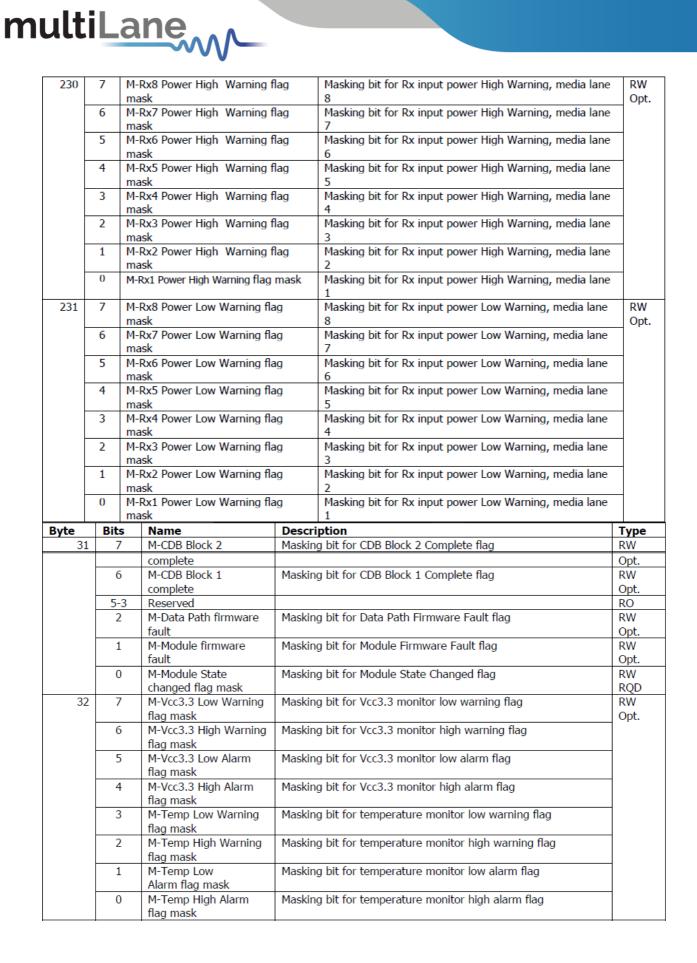

The table below shows the corresponding MSA mapping for the interrupt flags.

| Byte | Bits | Name                                                 | Description                                                                        | Тур       |

|------|------|------------------------------------------------------|------------------------------------------------------------------------------------|-----------|

| 213  | 7    | M- Data Path State Changed flag<br>mask, host lane 8 | Masking bit for Data Path State Changed flag, host lane 8                          | RW<br>RQD |

| ŀ    | 6    | M-Data Path State Changed flag                       | Masking bit for Data Path State Changed flag, host lane 7                          |           |

|      | 0    | mask, host lane 7                                    | Masking bit for Data Path State Changed hag, nost lane 7                           |           |

| ŀ    | 5    | M-Data Path State Changed flag                       | Masking bit for Data Path State Changed flag, host lane 6                          | -         |

|      | 5    | mask, host lane 6                                    | Hasking bit for Data Path State changed hag, host lane o                           |           |

| ŀ    | 4    | M-Data Path State Changed flag                       | Masking bit for Data Path State Changed flag, host lane 5                          | 1         |

|      | т    | mask, host lane 5                                    | Hasking bit for Data Path State Changed hag, host lane 5                           |           |

| ŀ    | 3    | M-Data Path State Changed flag                       | Masking bit for Data Path State Changed flag, host lane 4                          | 1         |

|      | 5    | mask, host lane 4                                    | Hasking bit for Data Path State Changed hag, host lane 4                           |           |

| ŀ    | 2    | M-Data Path State Changed flag                       | Masking bit for Data Path State Changed flag, host lane 3                          | 1         |

|      | 2    | mask, host lane 3                                    | Plasking bit for bata r aut state changed hag, host lane s                         |           |

| ŀ    | 1    | M-Data Path State Changed flag                       | Masking bit for Data Path State Changed flag, host lane 2                          | 1         |

|      | 1    | mask, host lane 2                                    | Plasting bit for bata rath state changed hag, host lane z                          |           |

| ŀ    | 0    | M-Data Path State Changed flag                       | Masking bit for Data Path State Changed flag, host lane 1                          | 1         |

|      | 0    | mask, host lane 1                                    | Plasking bit for bata r att state changed hag, host lane 1                         |           |

| 214  | 7    | M-Tx8 Fault flag mask                                | Masking bit for Tx Fault flag, media lane 8                                        | RW        |

| 211  | 6    | M-Tx7 Fault flag mask                                | Masking bit for Tx Fault flag, media lane 7                                        | Opt       |

| ŀ    | 5    | M-Tx6 Fault flag mask                                | Masking bit for Tx Fault flag, media lane 6                                        |           |

| ŀ    | 4    | M-Tx5 Fault flag mask                                | Masking bit for Tx Fault flag, media lane 5                                        | 1         |

| ŀ    | 3    | M-Tx4 Fault flag mask                                | Masking bit for Tx Fault flag, media lane 4                                        | 1         |

| ŀ    | 2    | M-Tx3 Fault flag mask                                | Masking bit for Tx Fault flag, media lane 3                                        | 1         |

| ŀ    | 1    | M-Tx2 Fault flag mask                                | Masking bit for Tx Fault flag, media lane 2                                        | 1         |

| ŀ    | 0    | M-Tx1 Fault flag mask                                | Masking bit for Tx Fault flag, media lane 1                                        | 1         |

| 215  | 7    | M-Tx8 LOS flag mask                                  | Masking bit for Tx LOS flag, lane 8                                                | RW        |

| 215  | 6    | M-Tx7 LOS flag mask                                  | Masking bit for Tx LOS flag, lane 7                                                | Opt       |

| ŀ    | 5    | M-Tx7 LOS flag mask                                  | Masking bit for Tx LOS flag, lane 7<br>Masking bit for Tx LOS flag, lane 6         |           |

| ŀ    | 4    | M-Tx5 LOS flag mask                                  | Masking bit for Tx LOS flag, lane 5                                                | -         |

| ŀ    |      |                                                      |                                                                                    | -         |

| ŀ    | 3    | M-Tx4 LOS flag mask<br>M-Tx3 LOS flag mask           | Masking bit for Tx LOS flag, lane 4<br>Masking bit for Tx LOS flag, lane 3         | -         |

| ŀ    |      | M-Tx3 LOS flag mask                                  |                                                                                    | -         |

| ŀ    | 1 0  |                                                      | Masking bit for Tx LOS flag, lane 2                                                | -         |

| 210  |      | M-Tx1 LOS flag mask                                  | Masking bit for Tx LOS flag, lane 1                                                | DW        |

| 216  | 7    | M-Tx8 CDR LOL flag mask                              | Masking bit for Tx CDR LOL flag, lane 8                                            | RW        |