# ML4003BX BERT | User Guide

Installation | Connection | Measurement

User Manual Revision 1.0, October 2021

Innovation for the next generation

#### **Notices**

Copyright © MultiLane Inc. All rights reserved. Licensed software products are owned by MultiLane Inc. or its suppliers and are protected by United States copyright laws and international treaty provisions.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013, or subparagraphs (c)(1) and (2) of the Commercial Computer Software -- Restricted Rights clause at FAR 52.227-19, as applicable.

MultiLane Inc. products are covered by U.S. and foreign patents, issued and pending. Information in this publication supersedes that in all previously published material. Specifications and price change privileges reserved.

#### **General Safety Summary**

Review the following safety precautions to avoid injury and prevent damage to this product or any products connected to it. To avoid potential hazards, use this product only as specified.

Only qualified personnel should perform service procedures.

While using this product, you may need to access other parts of the system. Read the General Safety Summary in other system manuals for warnings and cautions related to operating the system.

#### To Avoid Fire or Personal Injury

**Use Proper Power Cord.** Only use the power cord specified for this product and certified for the country of use.

**Observe All Terminal Ratings.** To avoid fire or shock hazard, observe all ratings and markings on the product. Consult the product manual for further ratings information before making connections to the product.

Do not apply a potential to any terminal, including the common terminal that exceeds the maximum rating of that terminal.

#### Do Not Operate Without Covers.

Do not operate this product with covers or panels removed.

**Avoid Exposed Circuitry.** Do not touch exposed connections and components when power is present.

#### Do Not Operate with Suspected Failures.

If you suspect there is damage to this product, have it inspected by qualified service personnel.

Do Not Operate in Wet/Damp Conditions. Do Not Operate in an Explosive Atmosphere. Keep Product Surfaces Clean and Dry

Caution statements identify conditions or practices that could result in damage to this product or other property.

# Table of Contents

| Notices 2                                       |

|-------------------------------------------------|

| Table of Contents   3                           |

| Revision Control                                |

| List of Acronyms                                |

| Introduction                                    |

| Installation                                    |

| Connecting to the Instrument9                   |

| Connection                                      |

| Measurement                                     |

| BERT Configuration                              |

| PRBS Pattern Configuration                      |

| Eye Shaping16                                   |

| Error Insertion16                               |

| CTLE Configuration17                            |

| Bit Error Ratio Reading17                       |

| BER                                             |

| Real Time BER                                   |

| Jitter Tolerance Test 19                        |

| Bit Error Ratio analysis 20                     |

| Bathtub configuration                           |

| Eye Contour                                     |

| Mask test 22                                    |

| Vertical Bathtub 22                             |

| Burst Mode 22                                   |

| DSO Configuration                               |

| DSO GUI                                         |

| Filters                                         |

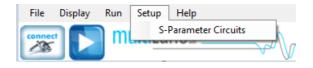

| S Parameter Mode 30                             |

| Frequency Domain Mode                           |

| Appendix 1 – Adding the ML4003BX to the Network |

| multiLane                 |  |

|---------------------------|--|

| Figure 1 GUI Installation |  |

| Figure 1 GUI Installation                      | 8  |

|------------------------------------------------|----|

| Figure 2 Connection Window                     | 9  |

| Figure 3 Connection Failure                    | 10 |

| Figure 4 ML4003BX Faceplate                    | 11 |

| Figure 5 BERT configuration                    | 13 |

| Figure 6 Rate Selection                        | 14 |

| Figure 7 Clock Configuration                   | 14 |

| Figure 8 PRBS setting                          | 15 |

| Figure 9 PRBS configuration                    | 15 |

| Figure 10 Eye Shaping sliders                  | 16 |

| Figure 11 Error insertion                      | 16 |

| Figure 12 CTLE                                 | 17 |

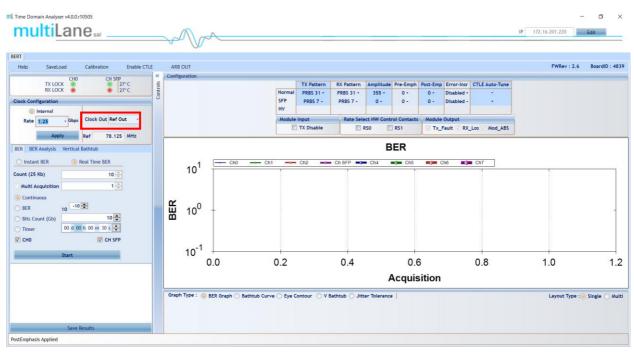

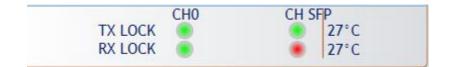

| Figure 13 Channels LEDs: Lock on CH0           | 17 |

| Figure 14 BER test                             | 18 |

| Figure 15 JTOL modes of operation              | 19 |

| Figure 16 Bathtub plot                         | 20 |

| Figure 17 Bathtub Configuration                | 21 |

| Figure 18 Eye Configuration                    | 21 |

| Figure 19 Vertical Bathtub                     | 22 |

| Figure 20 ARB OUT selection                    | 23 |

| Figure 21 Burst mode pattern and period window | 23 |

| Figure 22 AAA AWG Pattern                      | 24 |

| Figure 23 CCC AWG Pattern                      | 24 |

| Figure 24 FF00 AWG Pattern                     | 25 |

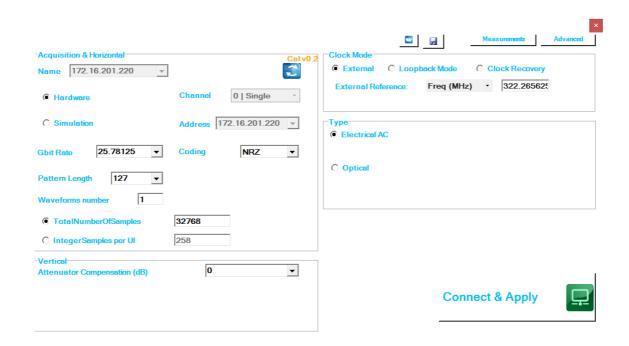

| Figure 25 DSO Configuration                    | 25 |

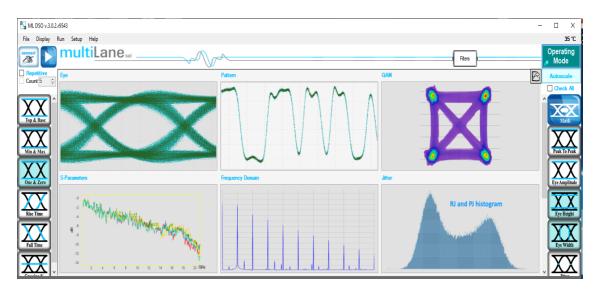

| Figure 26 DSO GUI                              | 26 |

| Figure 27 DSO Configuration window             | 27 |

| Figure 28 Operating modes                      | 28 |

| Figure 29 Eye diagram                          | 29 |

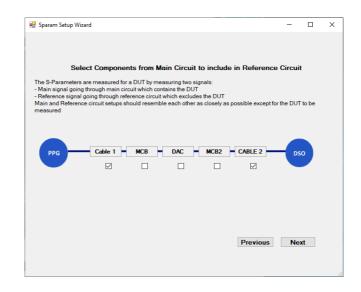

| Figure 30 S-Param setup                        | 32 |

| Figure 31: Setup Installation Procedure        |    |

| Errort Bookmark not defined                    |    |

Error! Bookmark not defined.

# **Revision Control**

| Revision number | Description                                           |

|-----------------|-------------------------------------------------------|

| 1.0.0           | <ul> <li>Initial Release, SW rev. 1.0 (HD)</li> </ul> |

| 1.1.0           | • SW rev. 4.0.0                                       |

# List of Acronyms

| Acronym | Definition                           |

|---------|--------------------------------------|

| BW      | Bandwidth                            |

| BERT    | Bit Error Rate Tester                |

| Conf    | Configuration                        |

| DUT     | Device Under Test                    |

| FEC     | Forward Error Correction             |

| FW      | Firmware                             |

| GBd     | Giga Baud                            |

| Gbps    | Gigabits per second                  |

| GUI     | Graphical User Interface             |

| HW      | Hardware                             |

| ISI     | Inter-symbol Interference            |

| JTOL    | Jitter Tolerance                     |

| NRZ     | Non-Return to Zero                   |

| PAM4    | Pulse Amplitude Modulation (4-level) |

| SI      | Signal Integrity                     |

| SNR     | Signal-to-Noise Ratio                |

| Sim     | Simulation                           |

| SW      | Software                             |

# Introduction

The ML4003BX is a state of the art, low cost PON tester consisting of a BERT, Digital Sampling Oscilloscope and an optical scope, all integrated in a compact 2U cPCI form factor. It supports burst mode PON by providing a programmable AWG output that can be programmed by the user to output a custom 64 bit TTL signal, synchronous to the high-speed data. The ML4003BX can be ordered as a low cost 16 Gbps Bit Error Ratio Tester with 32 GHz DSO and can be expanded to include a 10G / 25GHz Optical sampling scope. The full-fledged configuration contains in addition to the BERT, a 32 GHz (50GHz optionally) DSO, one SFP28 or one XFP port in addition to a 25 GHz (Optionally 10 GHz for a lower cost) optical sampling oscilloscope.

In the following user manual, a detailed explanation is provided to cover the installation, calibration and measurements performed on the ML4003BX.

# Installation

To install and start using the TDA interface for the first time, follow this step-by-step installation guide (with pictures) below:

- 1. *Run* the TDA setup file.

- 2. Install TDA.

- 3. *Connect* the ML BERT to the local network.

- 4. Launch the GUI.

- 5. *Start* the measurements.

After downloading the TDA setup file, select run and follow this easy step-by-step installation procedure:

| Image: Setup - ML-TDA-v4.0.0         −         ×                                                      | Image: Setup - ML-TDA-v4.0.0         −         ×                                                                |

|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Select Additional Tasks Which additional tasks should be performed?                                   | Ready to Install<br>Setup is now ready to begin installing ML-TDA on your computer.                             |

| Select the additional tasks you would like Setup to perform while installing ML-TDA, then click Next. | Click Install to continue with the installation, or click Back if you want to review or<br>change any settings. |

| Additional shortcuts:                                                                                 | Additional tasks:                                                                                               |

| Create a desktop shortcut                                                                             | Create a desktop shortcut                                                                                       |

|                                                                                                       |                                                                                                                 |

|                                                                                                       |                                                                                                                 |

|                                                                                                       |                                                                                                                 |

|                                                                                                       | v                                                                                                               |

|                                                                                                       | < >                                                                                                             |

| Next > Cancel                                                                                         | < Back Install Cancel                                                                                           |

Figure 1 GUI Installation

TDA should now be ready to run, with a shortcut button on the Desktop.

#### **Connecting to the Instrument**

To connect to the instrument, follow this sequence of steps:

- *Install* the ML-TDA GUI software.

- *Plug* the ML4003BX in the chassis.

- *Power Up* the ML4003BX.

- Connect the device to the network\* using a RJ45/LAN cable.

LAN connection can be validated with a ping to the static instrument IP.

- **Run** ML-TDA software.

- **Connect** using the IP address of the target instrument(s) (Figure 2). The IP address is printed on the back side of the instrument.

| Time Domain Analyser v4.0.0.r10505 | -     |     | $\times$ |

|------------------------------------|-------|-----|----------|

| multiLane sal 172.16.103.34        | Conne | ect | _        |

|                                    |       |     |          |

|                                    |       |     |          |

|                                    |       |     |          |

|                                    |       |     |          |

|                                    |       |     |          |

|                                    |       |     |          |

|                                    |       |     |          |

|                                    |       |     |          |

|                                    |       |     |          |

|                                    |       |     |          |

|                                    |       |     |          |

|                                    |       |     |          |

|                                    |       |     |          |

|                                    |       |     |          |

|                                    |       |     |          |

Figure 2 Connection Window

#### NOTES:

In the case of a connection failure, a pop-up message will appear indicating a connection error (Figure 3).

| III. Time Domain Analyser v4.0.0.r10505 |                                    | -     |     | × |

|-----------------------------------------|------------------------------------|-------|-----|---|

| multiLane 💷                             | P 172.16.103.34                    | Conne | ect |   |

| · · · · · · · · · · · · · · · · · · ·   |                                    |       |     |   |

|                                         |                                    |       |     |   |

|                                         |                                    |       |     |   |

|                                         | Could not connect to 172.16.103.34 |       |     |   |

|                                         |                                    |       |     |   |

|                                         |                                    |       |     |   |

|                                         |                                    |       |     |   |

|                                         |                                    |       |     |   |

|                                         |                                    |       |     |   |

|                                         |                                    |       |     |   |

|                                         | Disconnect                         |       |     |   |

|                                         |                                    |       |     |   |

|                                         |                                    |       |     |   |

|                                         |                                    |       |     |   |

|                                         |                                    |       |     |   |

Figure 3 Connection Failure

\*To add the device to the network, consult Appendix I at the end of this manual

# Connection

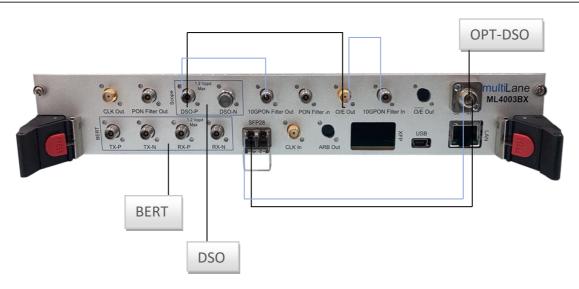

#### **BERT Connections**

To use the ML4003BX as a BERT, connect to the BERT pins.

- **TX-P and TX-N** are the transmitter pins

- **RX-P and RX-N** are the receiver pins

To use SFP28 or XFP transceiver, plug the transceiver in its corresponding port.

*CLK Out* is used when the user wants to generate a clock from the ML4003BX BERT.

#### **DSO Connections**

#### 1. Electrical DSO

To use the ML4003BX as an electrical DSO, connect to DSO-P and DSO-N pins.

#### 2. Optical DSO

To use the ML4003BX as an optical DSO:

- Connect optical cable to OPT In

- Connect O/E out to DSO-P or DSO-N and terminate the unconnected port with a 50 ohms termination (refer to the black lines in figure 4)

• To use PON or 10GPON filters, connect O/E out to PON Filter in or 10GPON Filter in, then connect PON Filter out or 10GPON Filter out to DSO-P or DSO-N and terminate the unconnected port (refer to the blue lines in figure4)

*CLK In* is used when the user wants to use an external clock.

# Measurement

Once connected to the instrument and the GUI, the ML4003BX can be configured as a BERT or DSO (Optical or Electrical) or BERT and DSO simultaneously.

# **BERT Configuration**

In order to use ML4003BX as a BERT, select BERT from the main window and click on configure.

| mL Time Domain Analyser v4.0.0.r10505 |                                            | - 1     | ×    |

|---------------------------------------|--------------------------------------------|---------|------|

| multiLane sai                         | IP 172.16.201.220                          | Connect | <br> |

|                                       |                                            |         |      |

|                                       |                                            |         |      |

|                                       |                                            |         |      |

|                                       | Connected to ML4003B at 172.16.201.220     |         |      |

|                                       | Choose the components that you want to use |         |      |

|                                       | BERT DSO                                   |         |      |

|                                       |                                            |         |      |

|                                       |                                            |         |      |

|                                       |                                            |         |      |

|                                       |                                            |         |      |

|                                       | Disconnect                                 |         |      |

|                                       |                                            |         |      |

|                                       |                                            |         |      |

|                                       |                                            |         |      |

|                                       |                                            |         | <br> |

Figure 5 BERT configuration

After configuring the instrument, run the desired configuration from the configuration window (Figure 5).

- 1. Select line Rate

- 2. Configure Clock Out

- 3. Set PRBS

Figure 6 Rate Selection

Figure 7 Clock Configuration

#### Figure 8 PRBS setting

\*Note that Normal is selected when using the BERT ports and SFP is selected when using SFP Port

## **PRBS Pattern Configuration**

- In the PRBS Configuration group box, select the pattern required; the available patterns are 7, 9, 15, 23, 31 and sinusoidal in addition to the 40 bits user pattern. TX Pattern tab is used for Configuring Generated signal, RX Pattern tab is used for pattern verification.

- To use the User defined capability, first select it from the Pattern combo box list, then in the text box specified for the User Defined write the sequence of bits you want. The sequence of bits should be in Hexadecimal only (16 bits length), ie FF, and then click the Set button.

- To make the TX off, choose the TX OFF

• In case the test engineer wired the positive TX channel to the negative RX channel by mistake, the software can compensate for this error by clicking on the invert button.

|   |            |          | TX Pattern | RX Pattern | Amplit |

|---|------------|----------|------------|------------|--------|

|   |            | Normal   | PRBS 31 -  | PRBS 31 •  | 411    |

|   | RX Pattern | PRBS 31  | •          | RX Invert  | 0-     |

|   |            | RX Patte | rn Select  |            | t HW C |

| _ |            |          | TA DISADIC |            | -50    |

Figure 9 PRBS configuration

The specified generator now starts generating a clean signal. If you would like to inject jitter to the signal generated to start shaping the eye diagram, you have to adjust the slide bars existing in the Eye Shaping group box (refer to the section Eye Shaping)

# **Eye Shaping**

This instrument includes 3 sliders to shape the form of the eye diagram, amplitude, Preemphasis and Post-emphasis. All slider values and other configurations are saved in the EPROM:

- Amplitude TX output amplitude is between 0mV and 800mV.

- **Pre Emphasis** TX output Pre-emphasis amplitude value could be changed from 0 to 15%.

- **Post Emphasis** TX output Signal Post-emphasis amplitude value could be changed from 0 to 31%.

| Amplitude | Pre-Emph | Post-Emp |

|-----------|----------|----------|

| 520 -     | 15 -     | 31 -     |

| 0 -       | 15 -     | 31 -     |

|           |          |          |

Figure 10 Eye Shaping sliders

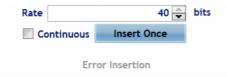

## **Error Insertion**

Error-Insr tab allows configuring signal error insertion. Rate select list allows the user to choose the amount of error bits. Rate will vary between 1 and 40 bits. Continuous checkbox allows continuously inserting error to the generated signal.

Figure 11 Error insertion

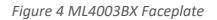

# **CTLE Configuration**

CTLE Tab allows the user to select the equalization level; CTLE varies from 0 to 10 dB to compensate for cable loss from the DUT to the BERT and to de-embed the system losses.

The auto adapt selects the best CTLE mode

|             |                        |                |             |          | ~             |   |       |          |            |                             |             |              |          |            |                |

|-------------|------------------------|----------------|-------------|----------|---------------|---|-------|----------|------------|-----------------------------|-------------|--------------|----------|------------|----------------|

| BERT        |                        |                |             |          |               |   |       |          |            |                             |             |              |          |            |                |

| Help        | SaveLoad               | Calibration    | Enable CTLE |          | ARB OUT       |   |       |          |            |                             |             |              |          |            |                |

|             | CH0                    | CH SFP         |             | «        | Configuration |   |       | _        |            |                             |             |              |          |            |                |

|             | TX LOCK 🔹<br>RX LOCK 😐 |                | 7°C<br>7°C  | Controls |               |   |       |          | TX Pattern | RX Pattern                  | Amplitude   | Pre-Emph     | Post-Emp |            | CTLE Auto-Tune |

|             | KA LUCK                | • 12           | //          | out      |               |   |       | Normal   | PRBS 31 +  | PRBS 31 +                   | 520 -       | 15 -         | 31 -     | Disabled • | -              |

| Clock Confi | guration               |                |             | Ŭ        |               |   |       | SFP      | PRBS 7 -   | PRBS 7 -                    | 0 -         | 15 -         | 31 -     | Disabled • | •              |

| ) Ir        | nternal                |                |             |          |               |   |       | HV       |            |                             |             |              |          |            |                |

| Rate        | 10 - Gbps              | Clock Out Rate | /2 -        |          |               |   |       | Module   | Input      | Rate Sele                   | ect HW Cont | rol Contacts | Module   | Output     |                |

|             |                        |                |             |          |               |   |       |          | TX Disable | TX Disable 📃 RS0 📃 RS1 🛛 Tx |             |              |          | ault 🔽 RX  | Los 🔽 Mod_ABS  |

|             | Apply                  | Ref 5000       | MHz         | ļ        |               |   |       | <u> </u> |            |                             |             |              |          |            |                |

| BER BER     | Analysis Vertical      | Bathtub        |             |          |               |   |       |          |            | J                           | itter T     | olerar       | nce      |            |                |

| 🔘 Mai       | nual 🔹                 | Automatic      | _           |          | 1             |   | - Ch1 | -        | Ch2 -      | Ch SFP                      |             |              |          |            |                |

|             |                        |                |             |          | 10'           | - |       |          |            |                             |             |              |          |            |                |

Figure 12 CTLE

#### **Bit Error Ratio Reading**

To be able to start BER measurements, the instrument ports should be in the loopback mode, which means TX port should be connected to the RX port.

To monitor the BER function, we have dedicated an LED to make sure it is locked.

- If the LED is green that means the RX is locked to the incoming data.

- If the LED is red that means the RX is not locked to the incoming data, which means there is a possibility that the cables are not connected correctly, thus try the invert function at the TX and RX sides; if the problem persists check the connections of your cables. The patterns of the Detector are automatically

modified when you change the generator pattern value.

Figure 13 Channels LEDs: Lock on CH0

# BER

BER test has the following configuration:

- Count (25kbit): Number of packets to be collected

- **Repeat Count:** if selected it allows you to choose the number of acquisitions. The measurements will be for the preceding configuration.

| BER BER Analysis  | Vertical Bathtub    |

|-------------------|---------------------|

| Instant BER       | 🔘 Real Time BER     |

| Count (25 Kb)     | 10 🖨                |

| Multi Acquisition | 1 🚔                 |

| Continuous        |                     |

| ) BER             | 10 -10 -10          |

| 🔘 Bits Count (Gb) | 10 💂                |

| Timer             | 00 d 00 h 00 m 30 s |

| 🔲 СНО             | CH SFP              |

|                   | Start               |

# **Real Time BER**

This feature allows the BERT to collect Real Time BER.

- Configuration Count (25kbit): Number of packets to be collected.

- **Repeat Count:** if selected it allows you to choose the number of acquisitions.

- **Continuous BER:** the BER value is repeated after each set the packet counts.

- **BER:** The BER test will run till it reaches the amount of BER selected. Timer: The BER test will run for the specified amount of time.

# **Jitter Tolerance Test**

Our user friendly JTOL tool, allows the user to perform automatic jitter injection for the stressed input applications and for characterization. This tool is featured in the BERT GUI (v.3.0.r3784 and above, MLBert\_A.dll r 3783). The tool needs MultiLane' ML407 clock synthesizer (up to 60 MHz) for multi-UI sinusoidal jitter generation and the ML4003BX. This option facilitates 10/40/100Gbps stressed input compliance testing. If you have an ML4003BX, you can use it to test your DUT's tolerance to Sinusoidal Jitter by either letting the GUI execute the test automatically according to the limits specified for CAUI4 or XLAUI4, or by self-defining the frequencies at which the test should be executed and the pass/fail criteria.

#### Modes of operation for the JTOL

Two modes of operation are featured and both require the clock synthesizer's input.

- Automatic mode: Features two masks, CAUI4 for high rate (25.78125Gbps) and XLAUI4 (10.3125Gbps) for low rate. Each test is performed based on the IEEE802.3bm- 2015 standards for high rate and IEEE802.3ba-2010 for low rate.

- **Manual mode:** The user can choose the desired frequency at which the sinusoidal jitter is generated, also specifying the desired UI interval.

| BER BER Analysis           | Vertical Bathtub              |

|----------------------------|-------------------------------|

| 🔘 Manual                   | <ul> <li>Automatic</li> </ul> |

|                            |                               |

|                            |                               |

|                            |                               |

| ) CAUI4                    | O XLAUI4                      |

| Target BER 10 <sup>^</sup> | -15 💂                         |

| BER Time                   | 10 Seconds                    |

| Ch 0 Start                 | Ch SF Start                   |

|                            |                               |

|                            | Start                         |

Figure 15 JTOL modes of operation

# multiLane

# **Bit Error Ratio analysis**

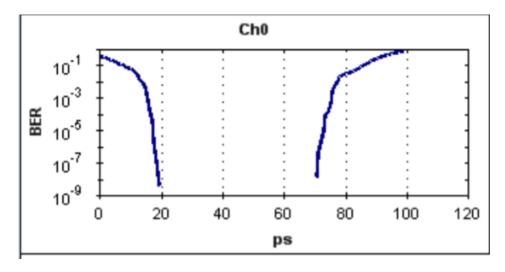

#### The Bathtub Plot

A viewpoint of jitter is provided by a bathtub plot, so named because its characteristic curve looks like the cross section of a bathtub. It is a graph of BER versus sampling point throughout the unit interval. It is typically shown with a log scale, which illustrates the functional relationship of sampling time to bit error ratio. Also, the deep eye width can be entered to get the BER level. When the sampling point is at or near the transition points, the BER is 0.5 (equal probability for success or failure of a bit transmission). The curve is flat in these regions, which are dominated by deterministic jitter mechanisms. As the sampling point moves inward from both ends of the unit interval, the BER drops off precipitously. These regions are dominated by random jitter mechanisms and the BER is determined by the sigma of the Gaussian processes producing the random jitter. As expected, the center of the unit interval provides the optimum sampling point. Note that there is BER measured for the middle sampling times.

#### Figure 16 Bathtub plot

Plotting the points on a graph of BER versus sampling location in time results in a curve that resembles the cross section of a bathtub, hence the term bathtub curve. A bathtub curve can be created either by software extrapolation from voltage over time measurement done by an oscilloscope, or by actually sampling the bits as done by a BERT. For development engineers, the final proof of performance of a component or subsystem is the direct measurement of BER at optimized timing and threshold levels employing error detection on every transmitted bit. However, the speed of the BER measurement is a function of the BER to be measured and the desired statistical confidence factor for the result.

# **Bathtub configuration**

To run the bathtub you should set the following configuration:

• **Target BER:** Select which level the Bathtub will reach. Upon selection, estimation of the time will be given.

- **Full sweep:** Read the BER at every point and allow the user to choose the start and stop time for the scan (time in mS). You can select a channel at a time to measure the Bathtub.

- **Dual Dirac:** Doesn't allow the user to choose the start and stop time for the scan

| BER          | BER Ana        | lysis | Vertical BathTub      |

|--------------|----------------|-------|-----------------------|

| ()<br>Target | Bathtub<br>BER | 10    | ⊙ Eye Contour •9      |

| Step T       | ime(mS):       |       | Full Sweep            |

| Start        |                | Stop  | Dual Dirac            |

|              |                | Cle   | ar All                |

| Сһ 0 1       | Start Ch 1     | Start | Ch 2 Start Ch 3 Start |

Figure 17 Bathtub Configuration

#### **Eye Contour**

#### Eye Contour Configuration

To run the Eye Contour you should set the following configuration:

• Accumulated: Select the number of data acquisitions. Upon selection, estimation of the time will be given. You can select a channel at a time to do the Eye Contour measurements.

| BER BER Analysis                                                           | Vertical Bathtub                                                                      |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| <ul> <li>Bathtub</li> <li>Target BER</li> <li>Estimated Time(m)</li> </ul> | Eye Contour<br>10 -7 C Fast Bathtub<br>S): 1s Full Sweep<br>Dual Dirac<br>Auto Offset |

|                                                                            | Clear All                                                                             |

Figure 18 Eye Configuration

#### Mask test

Masks typically represent an area in the eye opening that you want to ensure unit intervals do not fall within. The mask test is highly efficient since it quantifies both time and amplitude parameters in one measurement. The user should check the checkbox of the MASK to view the failing points, after specifying the X and Y values of every point in the mask.

## **Vertical Bathtub**

The V Bathtub allows the user to get the vertical Bathtub of a specific channel. The value entered in the textbox must be in ps, and according to the estimated time 2 s, the curve will be drawn. Also, the deep eye height can be entered to get the BER level.

| BER | BER Analysis                          | Vertical Bathtub   | JTOL       |

|-----|---------------------------------------|--------------------|------------|

|     | Horizontal Offset<br>Estimated Time 2 |                    | Dual Dirac |

|     |                                       | Clear All          |            |

|     | Ch 0 Start Ch 1                       | Start Ch 2 Start C | th 3 Start |

|     | Те                                    | est All Channels   |            |

Figure 19 Vertical Bathtub

## **Burst Mode**

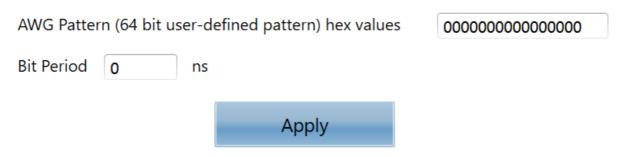

Burst mode allows the user to define the PPG signal and bits frequency. In order to enable Burst mode, ARB OUT is selected and AWG pattern is defined.

|                                                           |          | $\mathbf{V}$     |                          |                     |                                    |                                   |               |                             |                      |                          |                        |   |               |              |

|-----------------------------------------------------------|----------|------------------|--------------------------|---------------------|------------------------------------|-----------------------------------|---------------|-----------------------------|----------------------|--------------------------|------------------------|---|---------------|--------------|

| RT<br>Help SaveLoad Calibration Enable CTLE<br>CH0 CH SFP | < Confi  | OUT              |                          |                     |                                    |                                   |               |                             |                      |                          |                        |   | FWRev : 2.6   | BoardID : 48 |

| TX LOCK  Configuration                                    | Controls |                  |                          | Normal<br>SFP<br>HV | TX Pattern<br>PRBS 7 +<br>PRBS 7 - | RX Patter<br>PRBS 7 -<br>PRBS 7 - | 380 -         | de Pre-Empt<br>11 *<br>15 - | 12 •<br>12 •<br>31 • | Disabled +<br>Disabled + | LE Auto-Tune<br>•<br>• |   |               |              |

| Rate 10 Gbps Clock Out Ref Out  Apply Ref 156.25 MHz      |          |                  |                          | Module in           | iput<br>TX Disable                 |                                   | RS0           | ntrol Contact               |                      | Fault RX_Los             | Mod_ABS                |   |               |              |

| BER Analysis Vertical Bathtub                             |          |                  |                          |                     |                                    |                                   |               | BER                         |                      |                          |                        |   |               |              |

| Instant BER                                               |          | 10 <sup>1</sup>  | Ch0 Ch1                  |                     | ch2 👞                              | Ch SFP                            | Ch4           | Ch5                         | NÇ.                  | Ch6 Ch                   | h7                     |   | -             |              |

| Continuous         6ER         10         -10        10   | BER      | 10 <sup>0</sup>  | _                        |                     |                                    |                                   |               |                             |                      |                          |                        |   |               | -            |

| CHO CH SFP                                                |          | 10 <sup>-1</sup> |                          |                     |                                    |                                   |               |                             |                      |                          |                        |   |               |              |

| Start                                                     |          | 0                | .0                       | 0.2                 |                                    | 0.4                               |               | 0.                          | 6                    | 0                        | .8                     | 1 | 1.0           | 1.           |

|                                                           |          |                  |                          |                     |                                    |                                   |               | Acqui                       | sition               |                          |                        |   |               |              |

|                                                           |          | -                | ER Graph 🔘 Bathtub Curve | Eve Co              |                                    | athtub 🔿 .                        | litter Tolera | ice                         |                      |                          |                        |   | Layout Type : | Single 🔿 Mu  |

Figure 20 ARB OUT selection

ARB\_OUT – 🗆 🗙

# AWG Burst Control Signal (TTL) 200 MHz max

Figure 21 Burst mode pattern and period window

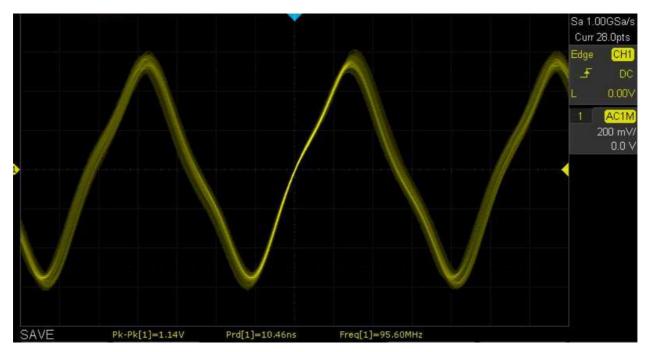

Figure 22 AAA AWG Pattern

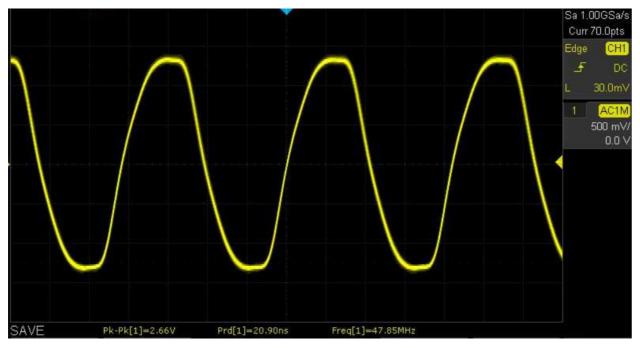

Figure 23 CCC AWG Pattern

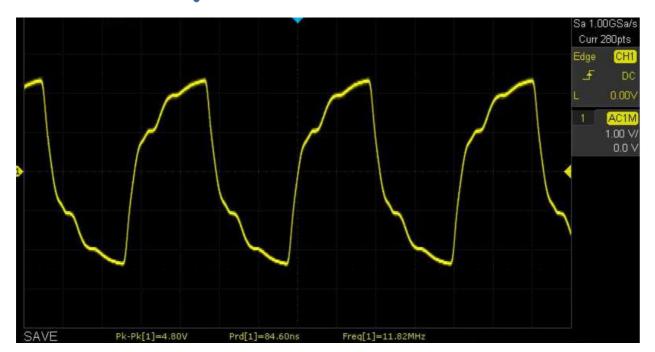

Figure 24 FF00 AWG Pattern

# **DSO Configuration**

In order to use ML4003BX as DSO, select DSO from the main window and click on configure.

| ml Time Domain Analyser v4.0.0.r10505 |                            |                                |            |          | -     |     | × |

|---------------------------------------|----------------------------|--------------------------------|------------|----------|-------|-----|---|

| multiLane 💷                           | $\wedge$                   |                                | IP 172.16. | .201.220 | Conne | ect |   |

| · · · · · · · · · · · · · · · · · · · |                            |                                |            |          |       |     |   |

| dip                                   |                            |                                |            |          |       |     |   |

|                                       |                            |                                |            |          |       |     |   |

|                                       |                            |                                |            |          |       |     |   |

|                                       | Connected to MI            | L4003B at 172.16.201.220       |            |          |       |     |   |

|                                       | Choose the components that |                                |            |          |       |     |   |

|                                       | BERT                       | DSO                            |            |          |       |     |   |

|                                       |                            | Clock:                         |            |          |       |     |   |

|                                       |                            | External Looped back from BERT |            |          |       |     |   |

|                                       |                            | CDR                            |            |          |       |     |   |

|                                       |                            |                                |            |          |       |     |   |

|                                       |                            |                                |            |          |       |     |   |

|                                       | Disconnect                 | Configure                      |            |          |       |     |   |

|                                       |                            |                                |            |          |       |     |   |

|                                       |                            |                                |            |          |       |     |   |

|                                       |                            |                                |            |          |       |     |   |

|                                       |                            |                                |            |          |       |     |   |

Figure 25 DSO Configuration

#### Clock Configuration

To configure the DSO Clock, the user can select:

- *External* if a clock source is connected to the CLK In pin.

- Looped back from BERT if the ML4003BX is used as a BERT and DSO simultaneously.

- **CDR** if the user wants to enable CDR option.

| mL Time Domain Analyser v4.0.0./10505 |            | -                      |

|---------------------------------------|------------|------------------------|

| multiLane and                         |            | IP 172.16.201.220 Edit |

| 050                                   |            |                        |

| File Display Run Setup Help Filters   |            |                        |

| 1000                                  | Title      | Operating<br>Mode      |

|                                       |            | Autoscalo              |

| Count 5 = 000                         |            |                        |

|                                       |            |                        |

|                                       |            | Mask                   |

|                                       |            |                        |

| XX                                    |            | XX                     |

| -200                                  |            | Peak To Peak           |

| XX 40                                 |            |                        |

| One & Zero -600                       |            | Eye Amplitude          |

|                                       |            | XX                     |

| Rise Time -1000 0 0.2 0.4 0.6         | 08 1 12 14 | 16 18 2 UI             |

|                                       |            |                        |

| Fall Time V                           | 0 ps, 0 mV | - Eve Heicht (M        |

| Markers Pattern                       |            |                        |

| C XHistogram                          |            |                        |

| C Y Histogram                         |            |                        |

| X (ps) Y (mV)                         |            |                        |

|                                       |            |                        |

|                                       |            |                        |

|                                       |            |                        |

|                                       |            |                        |

Figure 26 DSO GUI

## **DSO GUI**

• Click the connect button at the top left of your screen

10

- The "Connect to DSO" window will pop up

- Configure the DSO

Figure 27 DSO Configuration window

• Set the Line Rate

multiLane

- Enter the Pattern Length of the data feeding the DSO to capture the full pattern Note: Incorrect pattern length would still display the eye capture, however full pattern capture is required for certain features of the software such as Jitter Decomposition, PTB and Filters.

E.G.: Pattern Length = 127 for PRBS-7, The Pattern length of PN(n) is (2<sup>n</sup>) - 1.

- Specify clock mode:

- *External* for external clock source. In this case, the frequency or rate should be set.

- Loopback mode if the ML4003BX BERT is generating the signal.

- o Clock Recovery for CDR mode.

- Connect and apply.

\*For more details about DSO configuration refer to this link

#### **Operating Modes**

Figure 28 Operating modes

Selecting **Operating Modes** in upper right corner allows navigation between:

- Eye Measurement Mode:

- o Oscilloscope Measurements

- Multiple measurements

- o NRZ Measurements

- $\circ$  Mask Test

- Pattern Capture Mode including jitter decomposition

- S-Parameter Mode

- Frequency Domain Mode

#### Eye Measurement Mode

Regardless of hardware or simulation mode, it is possible to draw the eye and capture measurements after filling the configuration window and connecting to the instrument. In Eye Mode, in order to draw the eye diagram, click on the **Start Data Acquisition** button

Check the **Check All** button to view all the eye measurements down the screen for one time or select the needed measurement only by pressing on the desired icons. Use the second option to reduce measurement operation time.

Figure 29 Eye diagram

## **Filters**

The DSO GUI platform comes equipped with useful filters that offer a variety of signal processing techniques including cleaning the signal, de-embedding and discovering the optimal taps for improving an NRZ signal. The filtering GUI can be used to adaptively detect the minimum number of FFE or DFE taps required to reach a target Eye Height or SNR.

These filters can be applied to a DUT signal with or without introducing the **preserve noise** feature, which compensates for the filter side effect of reducing signal noise of adjacent measurement points.

Click on the Filters button after a successful signal acquisition. Current List of Supported Filters:

- 1- Moving Average Filter for signal smoothing: User can specify window size.

- 2- 4<sup>th</sup> Order Bessel Thomson filter at frequency equal to 0.75 of the bit rate (order and cutoff are configurable).

- 4- S2P/S4P De-Embedding: This filter simulates the inverse of a channel or DUT, where the channel's S2P or S4P file is loaded. Can also emulate channel insertion loss.

- 5- DFE: The Decision Feedback Equalizer (nonlinear adaptive equalizer) is based on the principle that once the decision circuit has determined the value of the current transmitted symbol, one can precisely remove the ISI contribution of that symbol to future received symbols. Optimal DFE parameters can be determined by the GUI, and it can also adaptively detect minimum taps required for a target Eye Height or SNR value.

- 6- FFE: With the Feed Forward Equalizer (linear equalizer), each value of the output sequence is a weighted sum of the most recent input values. Optimal FFE parameters can be determined by the software, and it can also adaptively detect minimum taps required for a target Eye Height or SNR value.

- 7- SIRC: Also referred to as SRC, stands for System Impulse Response Correction. It is the extracted time domain impulse response of a reference O/E which is converted into the frequency domain using an FFT. Two methods with which this file is generated are discussed in detail in Appendix IV. Either method will yield a 4<sup>th</sup> Order Bessel-Thompson roll-off as dictated by the IEEE 802.3bs/cd publication standards for both NRZ and PAM4 optical signals.

\*For more details about filters refer to this link

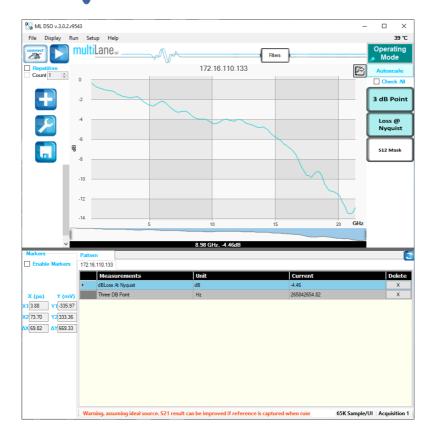

## **S** Parameter Mode

multiLane

The MultiLane DSO is now capable of measuring insertion loss S-parameters. Depending on how the DSO is connected, the user should be able to measure either of S21 dd, S12 dd, S21, S12, S43, S34, etc.

The only difference between all the above is:

- 1. Single ended vs. differential connection.

- 2. The direction in which the DUT is connected for S-param capture.

- 3. The ports in use when connecting the DUT via a single ended connection.

The approach used consists of the following steps:

- 1. Define Circuits:

- a. Main Circuit: Contains the DUT whose S-parameters are to be captured.

- b. Reference Circuit:

- i. Excludes the DUT whose S-parameters are to be captured.

- ii. Is as identical as possible to the Main Circuit, except for the DUT.

- iii. May require an additional component, such as a through, to be placed in the location of the DUT to close the circuit.

- 2. Set up the PPG:

- a. PRBS 7 or 9, PRBS9 is recommended.

- b. Maximum bit-rate possible (For maximum frequency range in the result)

- c. Cleanest possible Eye: This sometimes translates to maximum amplitude to maximize SNR. However, be careful not to exceed the maximum amplitude supported by the MultiLane DSO without using attenuators.

#### Kindly note PPG settings and amplitudes should not be altered after this point.

- 3. Capture the reference signal: when having the optimal PPG settings as described above, and with the reference circuit connected, run the DSO S-Parameter Setup Wizard to capture reference data.

- 4. Without altering any of the PPG settings, connect the main circuit, simply connect the DUT where needed to switch from **Reference Circuit** to **Main Circuit**, and run in S-parameter mode, the S21 insertion loss result will be visible.

# For a constant PPG Source Signal, S21 Is calculated using the equation: Frequency Response of DUT = FFT (Main Circuit Signal) / FFT (Reference Circuit Signal)

5. Insertion loss can be saved in external .S21 or .DsoCirc files. These files contain both magnitude and phase information; however, phase information is not accurate in the sense that there will always be a linear shift in phase. These files with their magnitude and phase information can later be used in the DSO Software for de- embedding or DUT emulation.

#### Components in Use

- 1. Two pairs of cables.

- 2. Two Module Compliance Boards that support the DAC connector. MCB S-parameters will be required. Often S-parameter information is supplied by the vendor.

- 3. One DAC cable.

- 4. Two through connectors that can mate the cable pairs together. These connectors will be considered to have negligible insertion loss.

- 5. MultiLane DSO

- 6. Any PPG, in this example the MultiLane BERT was used.

#### First, Connect Your Reference Circuit Hardware

Begin with connecting the circuit you will use as reference circuit as follows: Connect PPG differentially to Cable Pair 1, to Throughs, to Cable Pair 2, then to the DSO PPG => Cables 1 => Through => Cables 2 => DSO.

#### Step 2, Configure your PPG for Cleanest Signal

- 1. Setup your PPG: Kindly refer to step 2 under "<u>S Parameter Mode</u>" found on page 30.

- 2. Observe the signal on the DSO after going through the 'Reference Circuit'. Tune the PPG settings, sometimes you need to alter emphasis settings, sometimes amplitudes, sometimes bit rates. The cleanest eye possible for the highest rate possible will yield the most accurate result.

- 3. Once PPG settings are finalized, note them down. Kindly note PPG settings should not be altered after this point

#### Step 3, Go Through the S-Parameter Wizard on the DSO

#### Connect to the DSO

This DSO should currently be reading the signal going through the reference circuit. Recommended settings include a packet size of 512 and SW-PTB enabled.

#### Go to S-Parameter Setup

Figure 30 S-Param setup

#### Select the DSO Connected

After selecting the DSO click 'New Setup'.

|                       |                                                |                                        |              |   | п |   |

|-----------------------|------------------------------------------------|----------------------------------------|--------------|---|---|---|

| 🖳 Sparam Setup Wizard |                                                |                                        |              | - |   | × |

|                       |                                                |                                        |              |   |   |   |

| S-Pa                  | rameters Mea                                   | asurement Se                           | tup          |   |   |   |

| 1-Choose from the     | below Connected [                              | )SO's                                  |              |   |   |   |

| 172.16.110.133 🗸 🗸    | (items in red do n                             | ot have Sparameters )                  |              |   |   |   |

| 2-Set up Sparamet     | ers on the chosen [                            | SO                                     |              |   |   |   |

| New Setup             | Load From File                                 | `````````````````````````````````````` | /            |   |   |   |

|                       |                                                |                                        |              |   |   |   |

|                       |                                                |                                        |              |   |   |   |

|                       |                                                |                                        |              |   |   |   |

|                       |                                                |                                        |              |   |   |   |

|                       | ne two circuits, the                           |                                        |              |   |   |   |

| reference circu       | s to be measured, a<br>it. It helps if you pre | pare your scope co                     | nnection for |   |   |   |

| car                   | turing the reference                           | e calibration signal                   |              |   |   |   |

|                       |                                                |                                        |              |   |   |   |

|                       |                                                |                                        |              |   |   |   |

|                       |                                                |                                        |              |   |   |   |

|                       |                                                |                                        |              |   |   |   |

#### Create Your Main Circuit

| Circuit Name | 172.16.110.133 | ]               |        |   |      |  |

|--------------|----------------|-----------------|--------|---|------|--|

| Component    |                | Add Circuit Com | ponent |   |      |  |

| PPG          |                | <br>Cable 1     |        |   | DSO  |  |

|              |                |                 |        |   | 030  |  |

|              |                |                 |        |   |      |  |

|              |                |                 |        | [ | Done |  |

|              |                |                 |        |   |      |  |

#### Add the Main Circuit Components

Load the S-parameters of the MCBs. These will be used to calculate the S-parameters of the DAC DUT.

| Sparam Setup Wiza |                | ain Circuit Definition                                    |         |    |     |  |

|-------------------|----------------|-----------------------------------------------------------|---------|----|-----|--|

|                   |                | an orcar beimaon                                          |         |    |     |  |

|                   |                |                                                           |         |    |     |  |

|                   |                |                                                           |         |    |     |  |

|                   |                |                                                           |         |    |     |  |

| Circuit Name      | 172.16.110.133 |                                                           |         |    |     |  |

|                   |                |                                                           |         |    |     |  |

| Component         |                | Add Circuit Component                                     |         |    |     |  |

|                   |                |                                                           |         |    |     |  |

|                   |                |                                                           |         |    |     |  |

|                   |                |                                                           |         |    |     |  |

| PPG               | Cable 1 MCP    |                                                           | BLE 2 🗕 | DS | 0   |  |

|                   |                | Right>                                                    |         |    |     |  |

|                   |                | <left< td=""><td></td><td></td><td></td><td></td></left<> |         |    |     |  |

|                   |                | Load S-Param 🕨                                            |         |    |     |  |

|                   |                | Rename 🕨                                                  |         |    |     |  |

|                   |                | Delete                                                    |         |    |     |  |

|                   |                | Item Negligible                                           |         |    |     |  |

|                   |                |                                                           |         |    |     |  |

|                   |                |                                                           |         | D  | one |  |

|                   |                |                                                           |         |    |     |  |

|                   |                |                                                           |         |    |     |  |

|                   |                |                                                           |         |    |     |  |

|                   |                |                                                           |         |    |     |  |

Proceed by clicking 'Done'.

#### Select Components from Main Circuit Present in Reference Circuit

Select Cables 1 and 2 and click Next.

# Add Through Connector in Reference Circuit Definition

When done, click next.

| 9               |                       | Sparam Se           | etup Wizard    |                           |            |          | - 🗆 🗙           |

|-----------------|-----------------------|---------------------|----------------|---------------------------|------------|----------|-----------------|

| Reference Circu | uit Step2: Is there a | a Component (e.g. 1 | hrough) that r | needs to b                | e Added to | the Refe | erence Circuit? |

| Circuit Name    | Main Circuit-ref      | Add Circuit Co      | mponent        |                           |            |          |                 |

| PPG             | Cable 1               | Cables 2            | Through        | Right>                    | DKO        |          |                 |

|                 |                       |                     |                | Load S<br>Renam<br>Delete |            | ,        |                 |

|                 |                       |                     | Pr             | evious                    | Done       |          |                 |

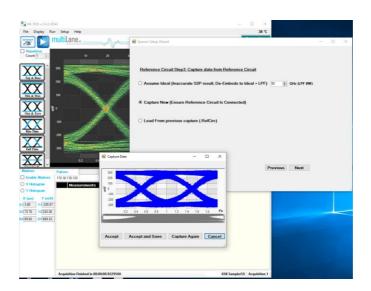

#### Capture Reference Data

Click 'Capture Now'

| d                                                         | -            | - 0 |  |

|-----------------------------------------------------------|--------------|-----|--|

| cuit Step3: Capture data from Reference Circuit           |              |     |  |

| al (Inaccurate S2P result, De-Embeds to Ideal + LPF) 50 🔅 | GHz (LPF BW) |     |  |

| v (Ensure Reference Circuit Is Connected)                 |              |     |  |

| previous capture (.RefCirc)                               |              |     |  |

|                                                           |              |     |  |

|                                                           |              |     |  |

| Previous                                                  | Next         |     |  |

| Previous                                                  | Next         |     |  |

The captured eye is depicted, the user can accept it or recapture.

Alternatively, the user may 'Accept and Save' the reference eye data. This will save the captured reference data for future use, allowing the user to call on 'Load from. RefCirc' in the future when visiting this page, hence avoiding reconnecting the reference circuit.

Click 'Next'

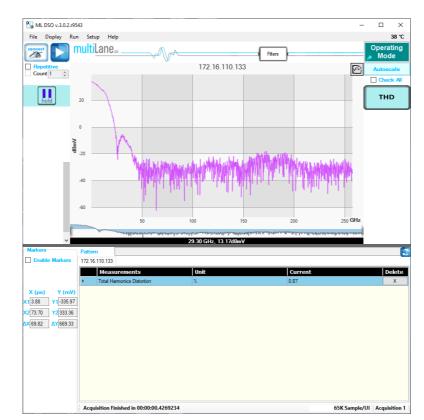

# **Frequency Domain Mode**

Upon moving to frequency domain mode, the frequency response can be plotted, and the total harmonic distortions can be calculated.

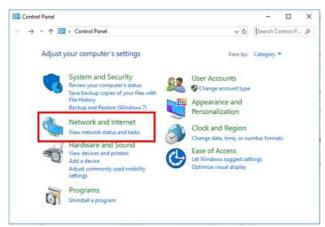

# Appendix 1 – Adding the ML4003BX to the Network

To create a local network connection, please follow these steps:

- **Create a local network connection** between the laptop and the ML4003BX using Internet Protocol Version 4 (TCP/IPv4).

- **Open** "Control Panel" and **choose** "Network and Internet".

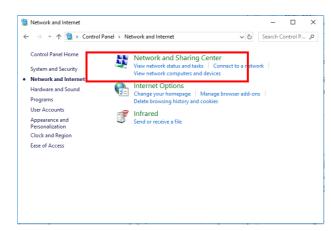

- o Open "Network and Sharing Center".

Click on "Change Adapter Settings", then choose "Local Area Connection".

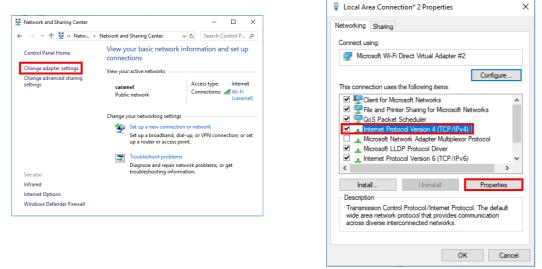

In the Networking Tab, click on "Internet Protocol Version 4 (TCP/IPv4)" then "Properties".

- Add a similar IP Address that shares a subnet with the instrument IP in the Advanced tab. This will be used to ping the instrument once the IP Address is changed to match that of the network.

- Connect the laptop directly to the ML4003BX using an Ethernet cable.

- Copy the IP Address found on the back of the unit.

- Ping the device to make sure that the connection is successful.

- Now a new local network has been successfully defined.

| Internet Protocol Version 4 (TCP/IPv4) Properties                                                                                                                                     |                     |   |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---|--|--|--|

| General                                                                                                                                                                               |                     | _ |  |  |  |

| You can get IP settings assigned automatically if your network supports<br>this capability. Otherwise, you need to ask your network administrator<br>for the appropriate IP settings. |                     |   |  |  |  |

| Obtain an IP address automatical                                                                                                                                                      | У                   |   |  |  |  |

| Use the following IP address:                                                                                                                                                         |                     |   |  |  |  |

| IP address:                                                                                                                                                                           | 172 . 16 . 101 . 10 |   |  |  |  |

| Subnet mask:                                                                                                                                                                          | 255.255.0.0         |   |  |  |  |

| Default gateway:                                                                                                                                                                      |                     |   |  |  |  |

| Obtain DNS server address automatically                                                                                                                                               |                     |   |  |  |  |

| Use the following DNS server addresses:                                                                                                                                               |                     |   |  |  |  |

| Preferred DNS server:                                                                                                                                                                 |                     |   |  |  |  |

| Alternate DNS server:                                                                                                                                                                 |                     |   |  |  |  |

| Validate settings upon exit                                                                                                                                                           | Advanced            |   |  |  |  |

|                                                                                                                                                                                       | OK Cancel           |   |  |  |  |

NOTE:

These steps are illustrated using Windows 10. Kindly note that previous versions of Windows have a similar procedure with slight differences in tabs or folders' names.

#### North America

48521 Warm Springs Blvd. Suite 310 Fremont, CA 94539, USA +1 510 573 6388

#### Worlwide

Houmal Technology Park Askarieh Main Road Houmal, Lebanon +961 81 794 455

#### Asia

7th Floor-2, No. 156 Sec. 2, Dongda Road, North District, Hsinchu City 300, Taiwan (R.O.C.) +886 3 5744 591

#### UAE

Building 4WA, Office 420 Dubai Airport Freezone Authority, Dubai, UAE +971 4 548 7 547